### A Systematic Approach for Obtaining Performance on Matrix-Like Operations

Submitted in partial fulfillment of the requirements for

the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

**Richard Michael Veras**

B.S., Computer Science & Mathematics, The University of Texas at Austin M.S., Electrical and Computer Engineering, Carnegie Mellon University

Carnegie Mellon University Pittsburgh, PA

August, 2017

Copyright © 2017 Richard Michael Veras. All rights reserved.

### Acknowledgments

This work would not have been possible without the encouragement and support of those around me. To the members of my thesis committee – Dr. Richard Vuduc, Dr. Keshav Pingali, Dr. James Hoe and my Advisor Dr. Franz Franchetti – thank you for taking the time to be part of this process. Your questions and suggestions helped shape this work. In addition, I am grateful for the advice I have received from the four of you throughout my PhD. Franz, thank you for being a supportive and understanding advisor. Your excitement is contagious and is easily the best part of our meetings, especially during the times when I was stuck on a difficult problem. You encouraged me to pursue project I enjoyed and guided me to be the researcher that I am today. I am incredibly grateful for your understanding and flexibility when it came to my long distance relationship and working remotely.

To the Spiral group past and present and A-Level, you are amazing group and community to be a part of. You are all wonderful friends, and you made Pittsburgh feel like a home. Thom and Tze Meng, whether we were talking shop or sci-fi over beers, our discussions have really shaped the way I think and approach ideas, and that will stick with me for a long time. I would also like to thank my undergraduate advisor Dr. Robert van de Geijn at the University of Texas. You saw my interest in research and did everything you could to get me to graduate school.

To my parents Elsa and Osvaldo Veras, my sister Sandra and brotherin-law Chris, thank you for always being there and encouraging me on my childhood dream of becoming a scientist. To my in-laws, Gail and Terry, you have always shown me kindness and support and for that I thank you. To my amazing and perfect wife, Dr. Lauren Elizabeth Grimley, your constant love and support got me through the toughest times. You really helped push me through, and I could not have done this without you. Thank you my princess.

The work in this dissertation was supported by the Defense Advanced Research Projects Agency (DARPA) under Contract No. FA8750-16-2-0033, FA8750-12-2-0291 and HR0011-13-2-0007, the United States Department of Defense (DoD) under Contract No. FA8702-15-D-0002 and the National Science Foundation (NSF) under Contract No. 1116802.

### Abstract

Scientific Computation provides a critical role in the scientific process because it allows us ask complex queries and test predictions that would otherwise be unfeasible to perform experimentally. Because of its power, Scientific Computing has helped drive advances in many fields ranging from Engineering and Physics to Biology and Sociology to Economics and Drug Development and even to Machine Learning and Artificial Intelligence. Common among these domains is the desire for timely computational results, thus a considerable amount of human expert effort is spent towards obtaining performance for these scientific codes. However, this is no easy task because each of these domains present their own unique set of challenges to software developers, such as domain specific operations, structurally complex data and ever-growing datasets. Compounding these problems are the myriads of constantly changing, complex and unique hardware platforms that an expert must target. Unfortunately, an expert is typically forced to reproduce their effort across multiple problem domains and hardware platforms.

In this thesis, we demonstrate the automatic generation of expert level high-performance scientific codes for Dense Linear Algebra (DLA), Structured Mesh (Stencil), Sparse Linear Algebra and Graph Analytic. In particular, this thesis seeks to address the issue of obtaining performance on many complex platforms for a certain class of matrix-like operations that span across many scientific, engineering and social fields. We do this by automating a method used for obtaining high performance in DLA and extending it to structured, sparse and scale-free domains. We argue that it is through the use of the underlying structure found in the data from these domains that enables this process. Thus, obtaining performance for most operations does not occur in isolation of the data being operated on, but instead depends significantly on the structure of the data.

### Contents

| 1 | Intr | roduction                                                                                                                                                          | 1 |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|   | 1.1  | A Motivating Example                                                                                                                                               | 2 |

|   | 1.2  | My Contributions                                                                                                                                                   | 4 |

| 2 | AN   | Method for High Performance                                                                                                                                        | 5 |

|   | 2.1  | Introduction                                                                                                                                                       | 5 |

|   | 2.2  | Preliminaries                                                                                                                                                      | 8 |

|   |      | 2.2.1 Domains                                                                                                                                                      | 3 |

|   |      | 2.2.2 Operations and Semirings                                                                                                                                     | ) |

|   |      | 2.2.3 An Overview of Modern Computer Architecture 10                                                                                                               | ) |

|   | 2.3  | A Method for Efficient Data Access                                                                                                                                 | 4 |

|   |      | 2.3.1 Partitioning the Data $\ldots \ldots \ldots$ | 4 |

|   |      | 2.3.2 A Nesting of Algorithms                                                                                                                                      | 7 |

|   |      | 2.3.3 Designing a Data Structure                                                                                                                                   | 1 |

|   |      | 2.3.4 The Power of a Data Layout Transformation 22                                                                                                                 | 2 |

|   | 2.4  | A Method for Fast Kernels                                                                                                                                          | 3 |

|   |      | 2.4.1 Selecting an Instruction Mapping                                                                                                                             | 4 |

|   |      | 2.4.2 Instruction Scheduling is Important                                                                                                                          | ŝ |

|   |      | 2.4.3 Further Optimizations and Code Generation 26                                                                                                                 | 3 |

|   | 2.5  | Chapter Summary 27                                                                                                                                                 | 7 |

| 3 | Rel  | ated Work 29                                                                                                                                                       | 9 |

|   | 3.1  | Introduction                                                                                                                                                       | 9 |

|   | 3.2  | Related Work                                                                                                                                                       | ) |

|   | 3.3  | Chapter Summary                                                                                                                                                    | 7 |

|   |      |                                                                                                                                                                    |   |

| т | Dense and | Structured | Applications | 39 |

|---|-----------|------------|--------------|----|

| L | Dense and | Structureu | Applications |    |

| 4 | Ma   | trix-Matrix Multiplication as Template for Performance | <b>41</b> |

|---|------|--------------------------------------------------------|-----------|

|   | 4.1  | Introduction                                           | 41        |

|   | 4.2  | Anatomy of a Gemm Micro-Kernel                         | 43        |

|   |      | 4.2.1 The Micro-Kernel                                 | 43        |

|   |      | 4.2.2 Decomposing the Outer-Product                    | 44        |

|   | 4.3  | Identifying Outer-Product Kernels                      | 46        |

|   |      | 4.3.1 The Building Blocks: SIMD Instructions           | 46        |

|   |      | 4.3.2 Mapping Unit Updates to SIMD Instructions        | 48        |

|   |      | 4.3.3 A family of Outer-Product Algorithms             | 49        |

|   | 4.4  | Selecting Outer-Product Kernels                        | 49        |

|   |      | 4.4.1 Estimating Throughput                            | 52        |

|   | 4.5  | Generating the Gemm Micro-Kernel                       | 53        |

|   |      | 4.5.1 A Work Flow for Kernel Generation                | 54        |

|   |      | 4.5.2 Embedding Functions Capture the Instruction-Mix  | 55        |

|   |      | 4.5.3 From Embedding Functions to Generated Code       | 58        |

|   |      | 4.5.4 Limits Imposed by Registers                      | 59        |

|   |      | 4.5.5 Scheduling and Tuning                            | 61        |

|   | 4.6  | Experimental Results                                   | 62        |

|   |      | 4.6.1 Analysis of Queueing Model                       | 67        |

|   |      | 4.6.2 Analysis of the Generated Kernels                | 69        |

|   |      | 4.6.3 Sensitivity to Parameters                        | 74        |

|   | 4.7  | Chapter Summary                                        | 77        |

| 5 | Stru | ucture Matters for Structured Mesh Computations        | 79        |

|   | 5.1  | Introduction                                           | 79        |

|   | 5.2  | Background                                             | 80        |

|   |      | 5.2.1 A Motivating Example                             | 80        |

|   | 5.3  | Theory                                                 | 84        |

|   |      | 5.3.1 Spacial Blocking                                 | 85        |

|   |      | 5.3.2 Temporal Blocking                                | 87        |

|   |      | 5.3.3 SIMD Vectorization                               | 93        |

|   | 5.4  | Mechanism                                              | 97        |

|   |      | 5.4.1 Kernel Generation                                | 97        |

|   | 5.5  | Experiments                                            | 105       |

|   |      | 5.5.1 Empirical Results                                | 105       |

|   |      | 5.5.2 Analytic Model                                   | 111       |

|   |      |                                                        |           |

| 5.6 | Chapter Summary |  |  |  |  |  |  |  |  |  |  |  |  | 113 |

|-----|-----------------|--|--|--|--|--|--|--|--|--|--|--|--|-----|

|     |                 |  |  |  |  |  |  |  |  |  |  |  |  |     |

### II Sparse and Unstructured Applications 115

| 6 | Hie  | rarchio | cal Data Structures Bridge the Dense-Sparse Pe  | er-   |

|---|------|---------|-------------------------------------------------|-------|

|   | form | nance   | Gap                                             | 117   |

|   | 6.1  | Introd  | luction                                         | . 117 |

|   |      | 6.1.1   | Our Contribution                                | . 118 |

|   | 6.2  | Propo   | sed Mechanism                                   | . 120 |

|   | 6.3  | Exper   | imental Setup and Analysis                      | . 127 |

|   |      | 6.3.1   | Performance Analysis                            | . 128 |

|   | 6.4  | Chapt   | er Summary                                      | . 131 |

| 7 | Rea  | d-Wor   | ld Networks Provide Sufficient Structure for Pe | er-   |

|   | form | nance   |                                                 | 133   |

|   | 7.1  | Introd  | luction                                         | . 133 |

|   | 7.2  | Theor   | y                                               | . 134 |

|   |      | 7.2.1   | Real-World Graphs                               | . 134 |

|   |      | 7.2.2   | Scale-Free Networks                             | . 135 |

|   |      | 7.2.3   | Hierarchical Clustering in Real-World Graphs    | . 136 |

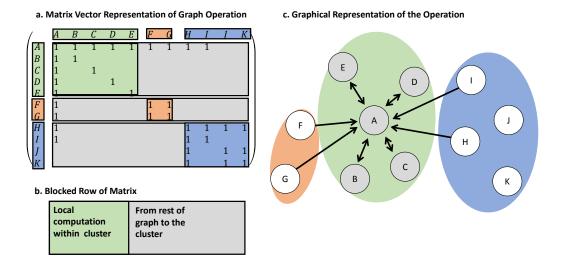

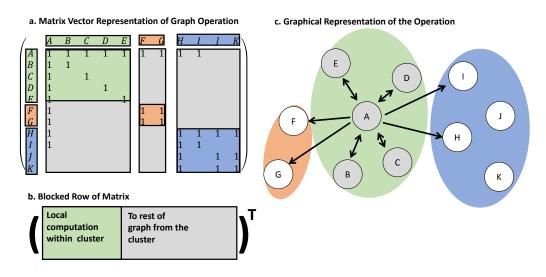

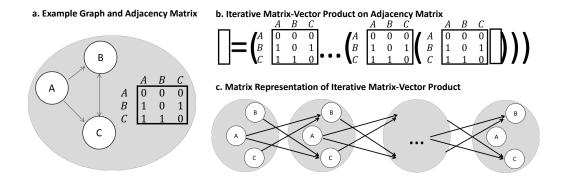

|   |      | 7.2.4   | Operations Over Graphs                          | . 137 |

|   |      | 7.2.5   | Graph Operations as Matrix Operations           | . 138 |

|   |      | 7.2.6   | Performance Enhancements for Graph Operations   | . 139 |

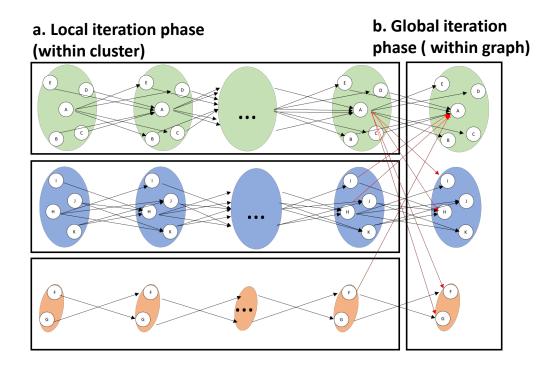

|   |      | 7.2.7   | Temporal Blocking for Graphs                    | . 141 |

|   |      | 7.2.8   | Spacial Blocking for Graphs                     | . 142 |

|   | 7.3  | Imple   | mentation of a High-Performance Graph Library   | . 143 |

|   |      | 7.3.1   | Generalized Hierarchical Sparse Framework       | . 144 |

|   |      | 7.3.2   | A High Performance spMV Implementation          | . 146 |

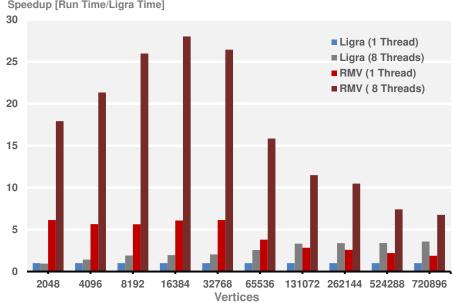

|   |      | 7.3.3   | Parallelism                                     | . 151 |

|   |      | 7.3.4   | Kernel Code Generation                          |       |

|   |      | 7.3.5   | A High Performance Graph Library                |       |

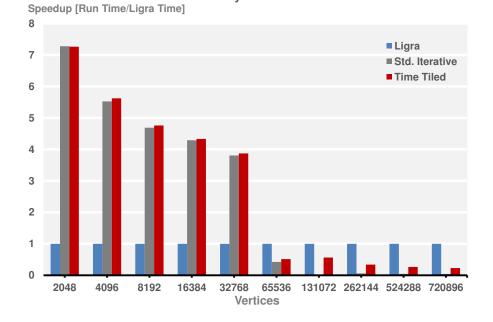

|   |      | 7.3.6   | Time Tiling for Graph Algorithms                | . 156 |

|   |      | 7.3.7   | Putting This All Together                       |       |

|   | 7.4  | -       | imental Evaluation                              | . 159 |

|   |      | 7.4.1   | Experimental Setup                              |       |

|   |      | 7.4.2   | Target Data Set                                 |       |

|   |      | 7.4.3   | Storing the Graph in the GERMV Object           | . 160 |

|     | 7.4.4 | Target Systems       |

|-----|-------|----------------------|

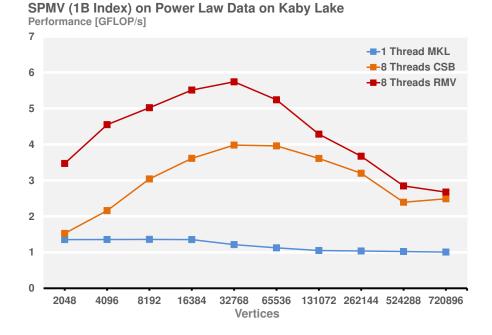

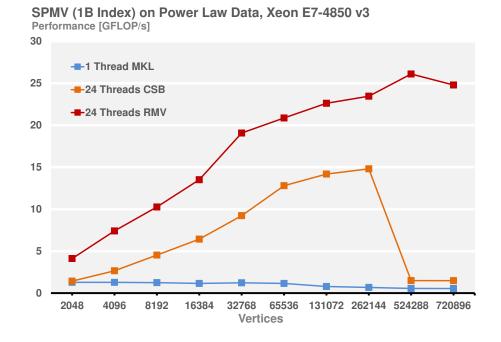

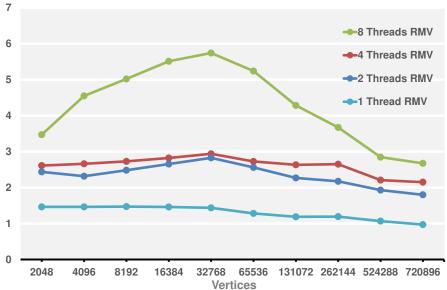

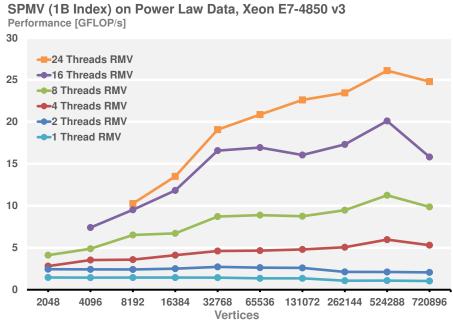

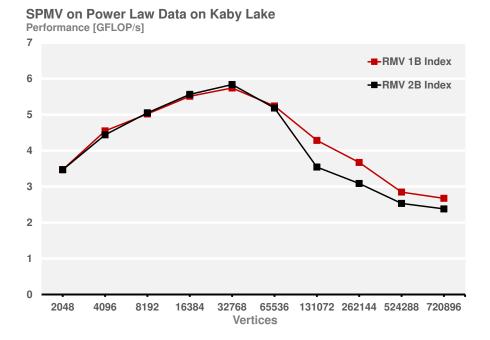

|     | 7.4.5 | Analysis of spMV     |

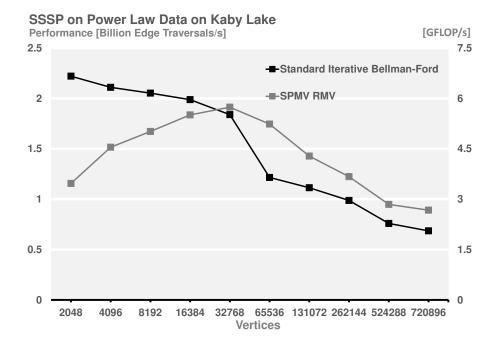

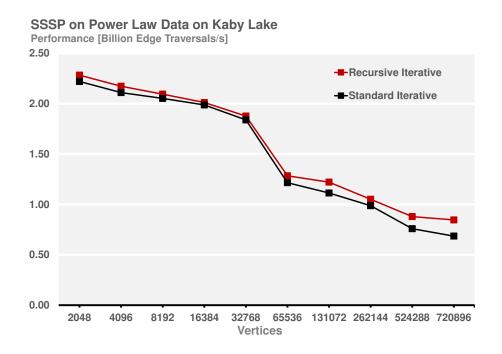

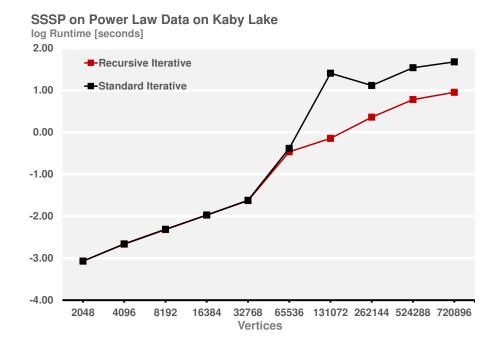

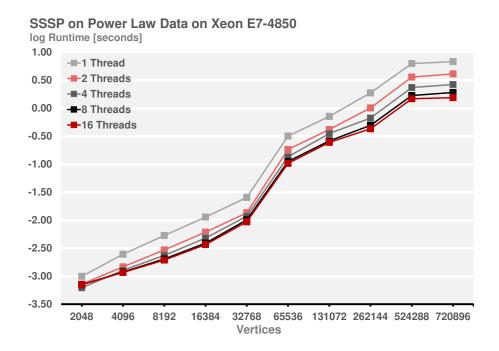

|     | 7.4.6 | Analysis of SSSP     |

|     | 7.4.7 | Analysis of Pagerank |

| 7.5 | Chapt | r Summary            |

### **III** Moving Forward

# 8 Summary 179 180 180 182 182 182 182 182 182 183 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 185 <th 185</

177

## List of Figures

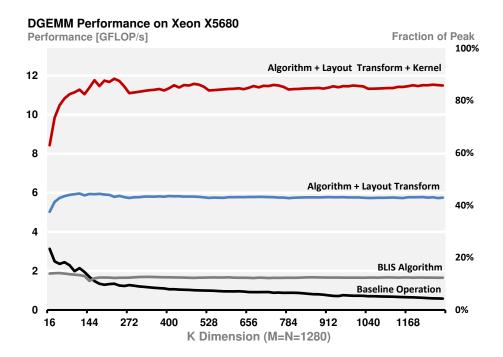

| 1.1  | Gemm performance breakdown                             | 3              |

|------|--------------------------------------------------------|----------------|

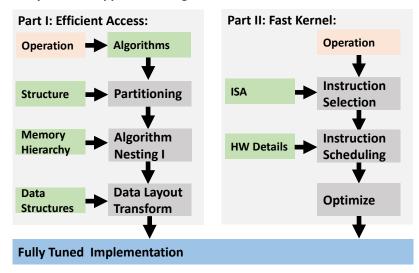

| 2.1  | A Mechanical Process for Performance                   | 6              |

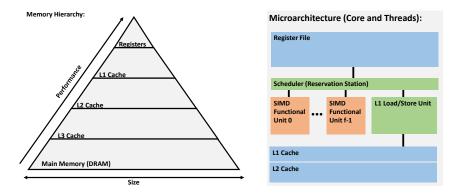

| 2.2  | A Simplified View of Modern Computer Architecture      | $\overline{7}$ |

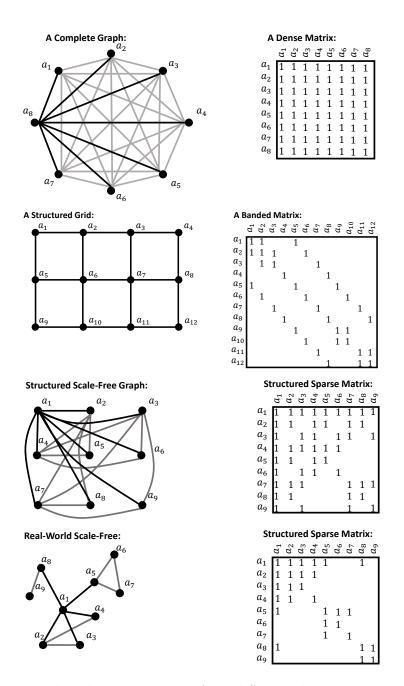

| 2.3  | Graphical and Matrix View of Structure in Domains      | 9              |

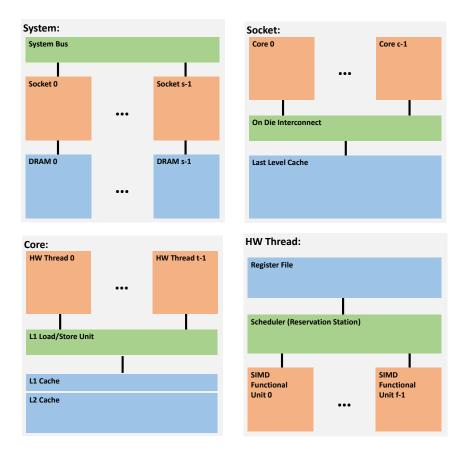

| 2.4  | An Overview of Modern Computer Architecture            | 12             |

| 2.5  | SIMD Functional Units                                  | 13             |

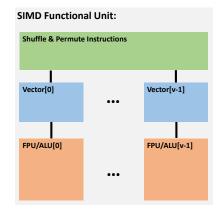

| 2.6  | Different Examples of Partitions                       | 15             |

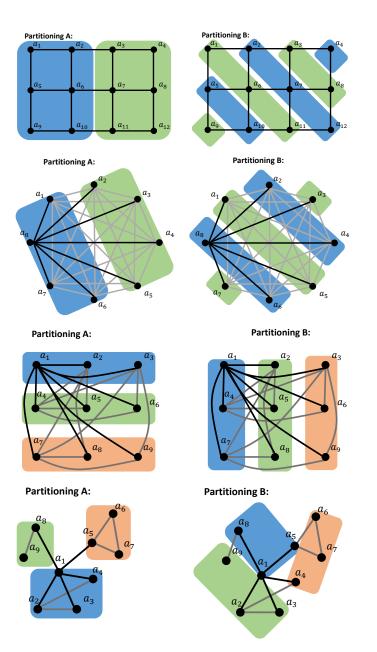

| 2.7  | Divide-and-Conquer Matrix-Vector Multiply              | 18             |

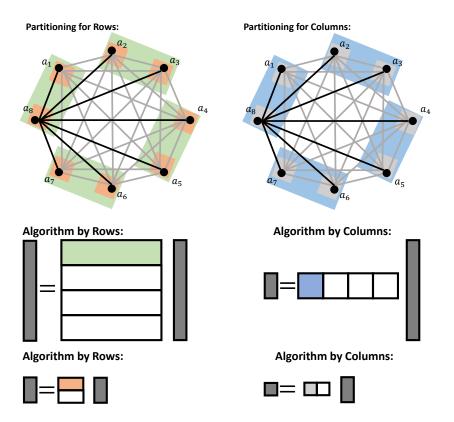

| 2.8  | Data Layout Transformation                             | 22             |

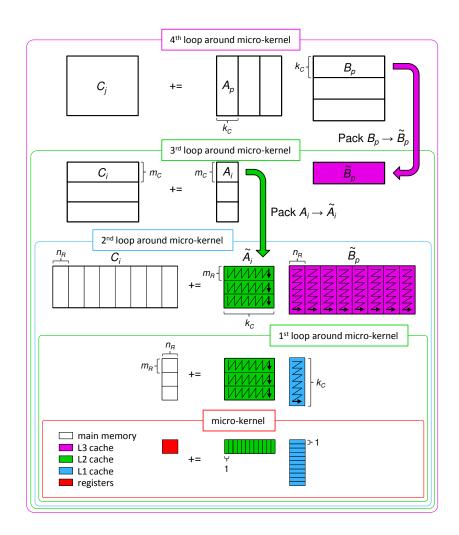

| 4.1  | The BLIS Algorithm                                     | 42             |

| 4.2  | An outer-product kernel                                | 46             |

| 4.3  | A SIMD outer-product                                   | 48             |

| 4.4  | A breakdown of unit-updates                            | 50             |

| 4.5  | Queue Model of Sandy Bridge Microarchitecture          | 52             |

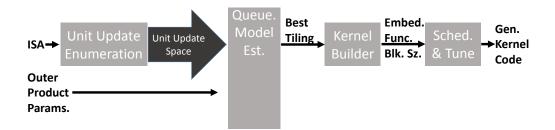

| 4.6  | Workflow for Generating gemm Kernels                   | 53             |

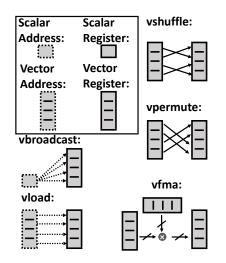

| 4.7  | SIMD Vector Instructions                               | 55             |

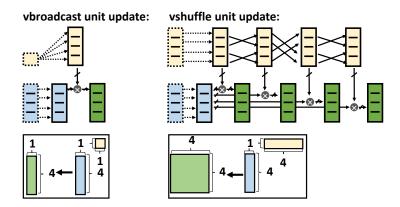

| 4.8  | SIMD Unit Updates                                      | 56             |

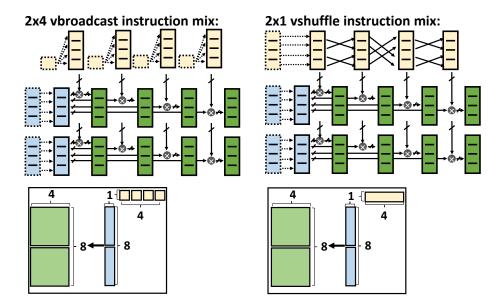

| 4.9  | Outer-Products from SIMD Unit Updates                  | 56             |

| 4.10 | Embedding Functions for Capturing Instruction Mixes    | 57             |

| 4.11 | Register Blocking for Outer Porducts                   | 59             |

| 4.12 | Skeleton of gemm Kernel                                | 60             |

|      | Generated Code Snippet for gemm Kernel                 | 62             |

| 4.14 | Experimental Evaluation of Queueing Model              | 70             |

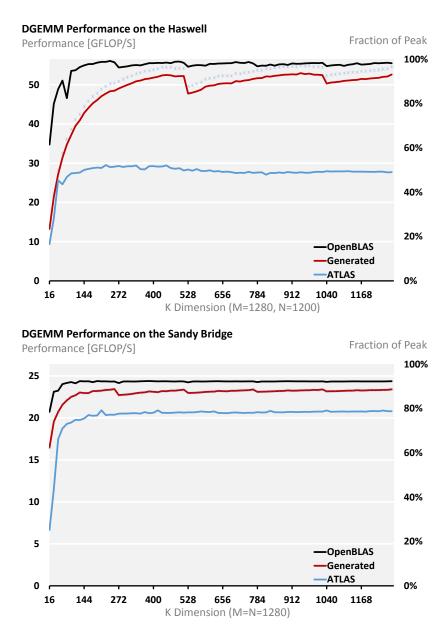

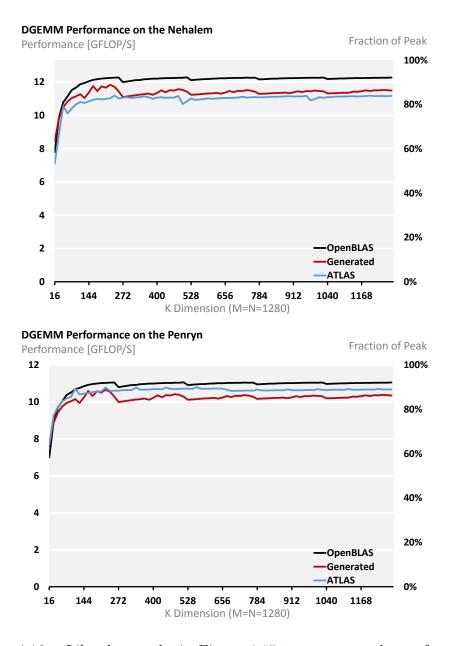

| 4.15 | Sequential Performance Comparison of Gemm Code, Part 1 | 71             |

| 4.16 | Sequential Performance Comparison of Gemm Code, Part 2 | 72             |

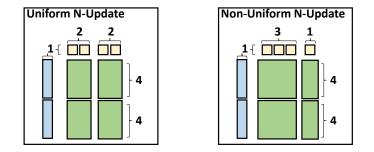

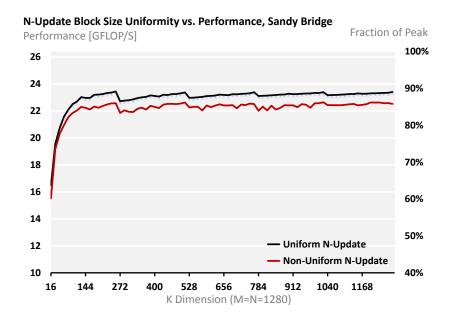

| 4.17 | Gemm Kernel Performance Sensitivity Study              | 73             |

| 4.18 | Gemm Kernel Sensitivity to N-Update Shape              | 73             |

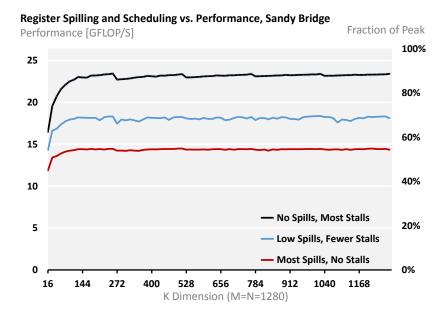

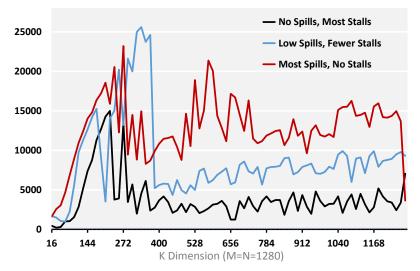

| 4.19 | Gemm Kernel Performance Sensitivity to Scheduling 75  |

|------|-------------------------------------------------------|

| 4.20 | Gemm Kernel Cache Miss Sensitivity to Scheduling 76   |

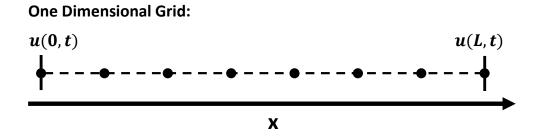

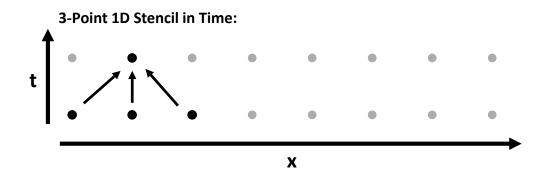

| 5.1  | Example Discretized Metal Rod                         |

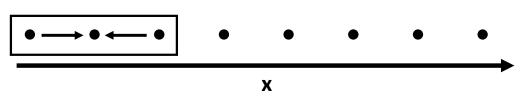

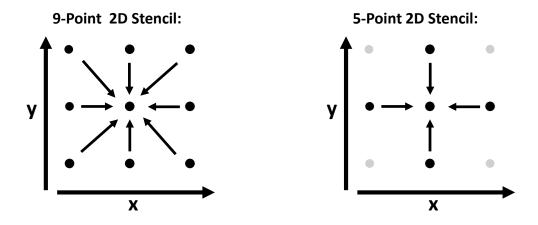

| 5.2  | Computing a Derivative Numerically                    |

| 5.3  | A Stencil with Multiple Time Steps                    |

| 5.4  | Two Dimensional Stencils                              |

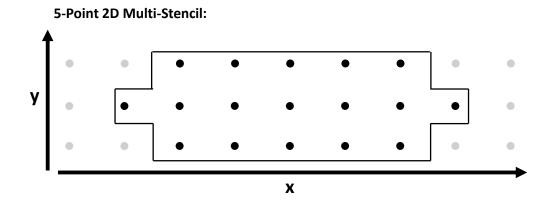

| 5.5  | A Multistencil                                        |

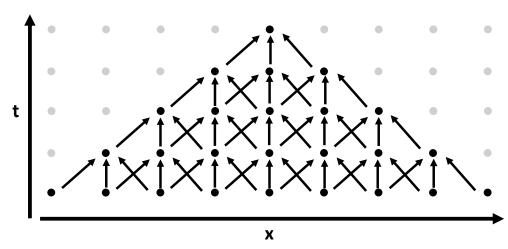

| 5.6  | Blocking in the Time Dimension                        |

| 5.7  | Overlapping Blocks                                    |

| 5.8  | Mixed Tile Shapes for Blocking                        |

| 5.9  | Upward and Downward Trapezoidal Tiles                 |

| 5.10 | SIMD Instructions on Stencils                         |

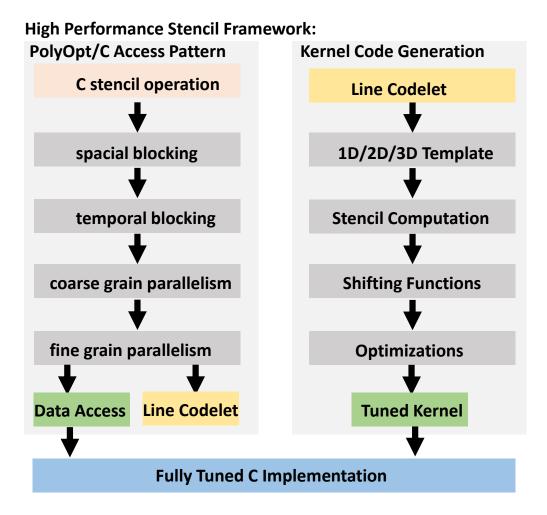

| 5.11 | Code Generator for Stencils                           |

| 5.12 | SIMD Shifting Function for SSE 2-Way                  |

| 5.13 | SIMD Shifting Function for SSE 4-Way                  |

| 5.14 | SIMD Shifting Function for AVX 40Way                  |

| 5.15 | SIMD Shifting Function for AVX 8-Way                  |

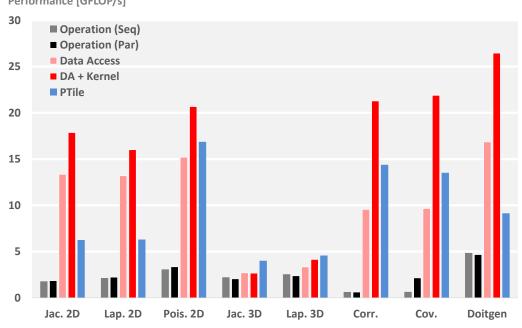

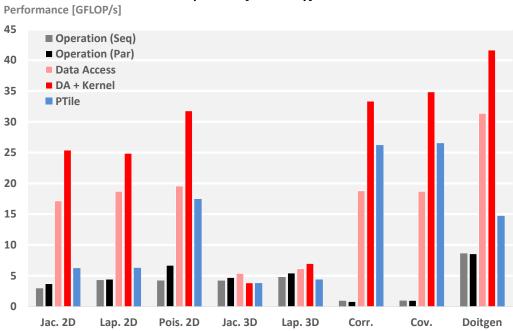

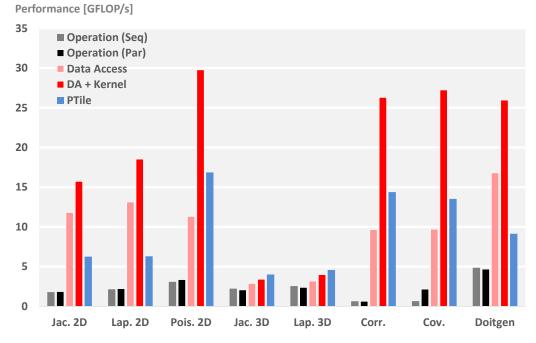

| 5.16 | SSE 2-Way Stencil Results                             |

| 5.17 | SSE 4-Way Stencil Results                             |

|      | AVX 4-Way Stencil Results                             |

| 5.19 | AVX 8-Way Stencil Results                             |

| 5.20 | Comparing our Performance Model to Empirical Data 112 |

| 6.1  | Cartoon of a Scale-Free Graph                         |

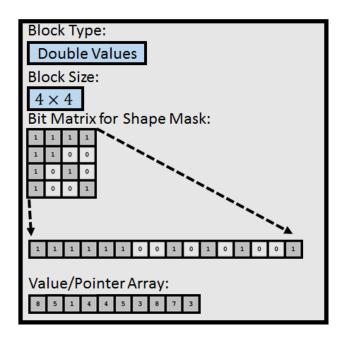

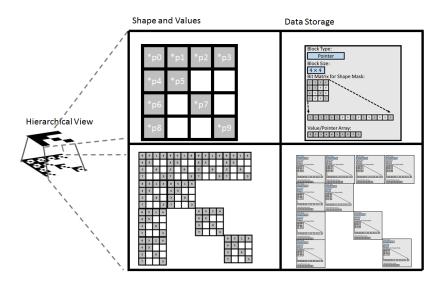

| 6.2  | Hierarchical Storage of Sparse Data                   |

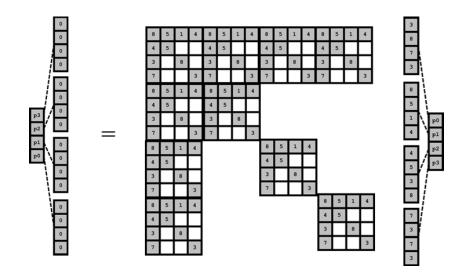

| 6.3  | An Instantiated Recursive Sparse Matrix               |

| 6.4  | Two Level Recursive Sparse Matrix                     |

| 6.5  | spMV Using Hierarchical Format                        |

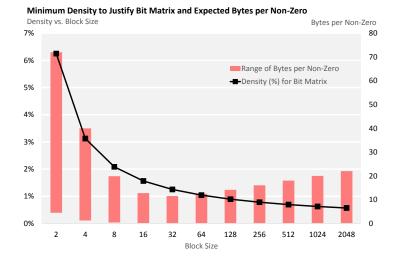

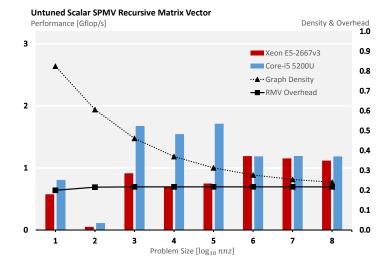

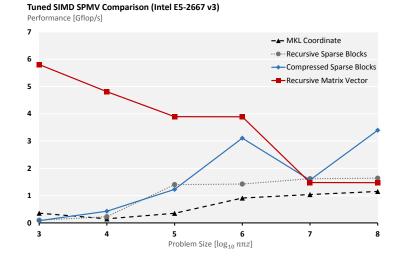

| 6.6  | Analysis of Data Density and Overhead                 |

| 6.7  | spMV Performance Evaluation                           |

| 6.8  | Tuned spMV Analysis                                   |

| 7.1  | Cartoon of a Scale-Free Graph                         |

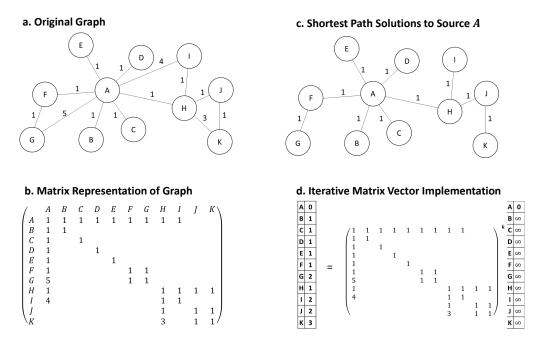

| 7.2  | Different Views for Graphs                            |

| 7.3  | SSSP as a Matrix Operation                            |

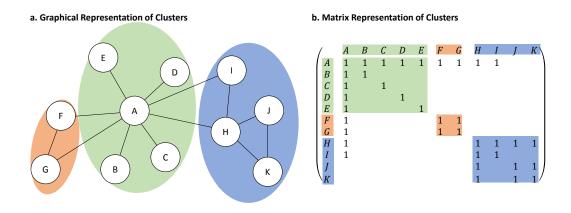

| 7.4  | Clusters in Scale-Free Graphs                         |

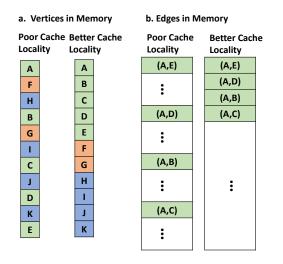

| 7.5  | Comparison of Graph Data Layout                       |

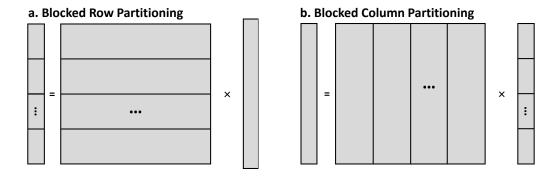

| 7.6  | spMV Algorithm Breakdown                              |

|------|-------------------------------------------------------|

| 7.7  | spMV Algorithm by Rows                                |

| 7.8  | spMV Algorithm by Columns                             |

| 7.9  | Iterative spMV                                        |

| 7.10 | Local Computation in a Graph                          |

| 7.11 | Time-Tiling Across a Graph                            |

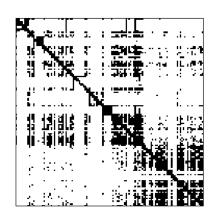

| 7.12 | Web Graph Used in Experiments                         |

| 7.13 | spMV Performance on Real Data                         |

| 7.14 | spMV Performance on a Large Machine                   |

| 7.15 | Performance Scaling on Small Machines                 |

|      | Performance Scaling on Large Machines                 |

| 7.17 | Performance Comparison of Different Encodings         |

| 7.18 | SSSP Performance Behavior                             |

| 7.19 | SSSP Throughput                                       |

| 7.20 | Time-Tiling Performance on Graphs                     |

|      | Parallel Performance of Time-Tiled Implementation 172 |

| 7.22 | SSSP Comparison Against Ligra                         |

| 7.23 | PageRank Comparison Against Ligra                     |

| 8.1  | A Mechanical Process for Performance                  |

| 8.2  | Metric Space View of Structured Data                  |

### List of Tables

| 2.1 | Matrix-like Operations                              |

|-----|-----------------------------------------------------|

| 2.2 | Semirings for Computations                          |

| 2.3 | Divide and Conquer Algorithms                       |

| 4.1 | Cache Details of Benchmark Machines                 |

| 4.2 | Microarchitectural Details of Benchmark Machines 64 |

| 4.3 | Queueing Model of gemm for Xeon Phi                 |

| 4.4 | Queueing Model on Sandy Bridge                      |

| 4.5 | Cache Blocking Dimensions                           |

| 4.6 | IACA Results Simulating Performance                 |

| 5.1 | Stencil Block Sizes for Experiments                 |

| 5.2 | Instruction Breakdown for Stencil Kernels           |

| 7.1 | Blocking Dimensions for GERMV Data Structure 161    |

| 7.2 | Hierarchical View of GERMV Data Structure           |

# Chapter 1 Introduction

Over the past seven decades, Scientific Computation joined the ranks of theoretical and experimental science as part of the three pillars of the scientific process. In this process, we make observations of natural phenomena and use the first pillar, theoretical, to deduce the underlying process in order to develop a theory. Using the second pillar, experimental, we test the accuracy of our theory. We then iterate over these steps to refine our theory until we get closer to the truth. However, we are limited in the experiments we can conduct in that they may be too large, too dangerous, too unrealistic to carry out, they may require a time scale that is too short or too long to be practical, or require time to flow backwards. The third pillar, Scientific Computation, addresses these limitations. Scientific queries are posed as mathematical operations which we implement as code and compute in order to obtain our answer. Problem size, time scale, and even the direction of time is no longer dependent on real world limitations. Instead these features are dependent on the computational power of the hardware and the ability of the scientific code to extract performance from that power. Thus, for Scientific Computation, obtaining performance from the code is key. This has been the driving force behind High Performance Computing (HPC), which is the science and application of producing high performance software and hardware. While much work has resulted in the automation of how we obtain performance, a perpetual frontier exists because we can only automate what we understand. Therefore, a great deal of performance is dependent on expert programmers who hand code and tune these application for every new piece of hardware.

The development of Scientific Computation has lead to the widespread availability of HPC resources and expertise. This has lead to ability to experimentally measure networks outside the original applications of HPC, such as those that arise in social, biological, financial, epidemiological, energy and transportation settings. In the same way that physics and engineering drove much of the early innovation in HPC, we see a rise in the use of computational techniques to answer questions in the natural and social sciences. Unlike the datasets collected from physics and engineering problems, the structure of these collections are seemingly irregular, hyper sparse and extremely large. Once again performance is critical in order to answer computational complex queries over these datasets. Thus not only has computation in the social sciences inherited the problems of HPC, but the complexity of their data has precluded the use of many existing HPC solutions. Is there a common class of problems between traditional scientific computing and big data where we can use the same performance techniques? And under what conditions are these techniques applicable on social science problems.

In this dissertation, I argue that if we have a matrix-like operation over structured data, then we can use the knowledge of this structure to produce a high performance implementation. More precisely, if we start with an operation that we can decompose into an efficient access pattern and compute core, then the dataset's structure allows us to determine two things: First, how to efficiently access and store the data in memory. Second, the structure determines how to specialize the computation to this problem. Thus, knowing the structure allows us to couple an efficient compute core to an efficient access to a high performance implementation of the original operation.

### **1.1** A Motivating Example

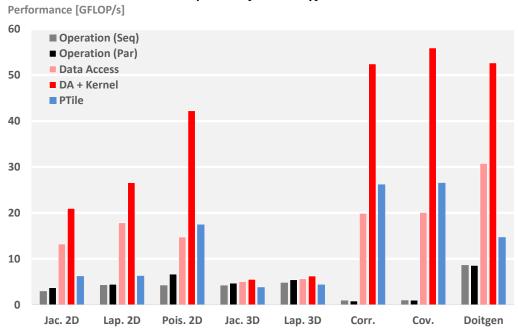

Alone, an efficient compute kernel or memory access pattern is not sufficient for performance, but rather both pieces are needed in tandem. We illustrate this in Figure 1.1 using a double precision matrix-matrix multiply (Gemm) as our example. This operation computes  $C = AB + \hat{C}$ , where  $A \in \mathbb{R}^{m \times k}$ ,  $B \in \mathbb{R}^{k \times n}$  and  $C, \hat{C} \in \mathbb{R}^{m \times k}$ . More precisely, it computes the following:

$$c_{i,j} = \sum_{p}^{k} a_{i,p} b_{p,j} + \hat{c}_{i,j}$$

(1.1)

Where each element  $c_{i,j}$  of C is the result of an inner-product between a row in A and a column in B.

Figure 1.1: Performance starts with finding the correct algorithm and ends with combining data layout transformations with efficient kernels.

In order to motivate this two part approach to performance, we will break an implementation of Gemminto multiple pieces: a baseline implementation, an efficient algorithm, an algorithm turned to an efficient access pattern, and the access pattern coupled with a fast kernel. We show this in Figure 1.1, we compare the performance versus the problem size of four implementations. The first implementation, baseline operation, directly implements equation 1.1 as three loops in C without any additional algorithmic transformations. This implementation sustains 10% of the machine's peak performance. The second implementation, BLIS Algorithm, uses 8 loops to implement the Gemm algorithm in [1, 2]. The additional looping allows for sustained performance at 15% of the machine peak. It does this by insuring that the cache hierarchy is effectively used. However, the additional loops incur a substantial indexing overhead, in order to access the input matrices. These matrices are not stored in an order that is amenable to the access pattern determined by the algorithm. To correct this, the implementation marked algorithm + layout transform, uses the same algorithm as the previous implementation, but performs a data layout transformation on the A and B matrices such that the algorithm accesses each element in unit stride. The kernel in this implementation is naively implemented and relies entirely on the compiler to extract performance. Overall this implementation achieves near 45% of the machine's peak. The final implementation, *algorithm* + *layout transform* + *kernel* achieves near 90% of peak by replacing the naive kernel from the previous implementation with a generated and tuned kernel for that machine.

From Figure 1.1, both the data layout transformation and an efficient kernel are necessary for performance, but they both depend on finding an efficient algorithm for the target operation on a given dataset. This approach sketches how we handle the other three domains targeted in this thesis, where we will split the problems in two parts (access and kernel) and optimize each part to the problem.

### **1.2** My Contributions

The goal of this work is to uncover the necessary techniques and transformations for systematically producing high performance code for Linear Algebra and similar operations. Specifically, my contributions are as follows:

- I generalize a two part method for performance, used in dense linear algebra, to a broader set of domains.

- I develop a systematic approach to generating high performance dense matrix-matrix multiplication kernel that matches or exceeds the performance of expert written kernels.

- I provide a method for generating efficient vectorized time-tiled stencil kernels for finite difference and similar structed mesh applications that perform near their theoretical peak.

- I implement a high performance Sparse Matrix-Vector multiplication for scale-free data using a hierarchical sparse data structure. This implementation outperforms the state of the art Sparse Matrix-Vector library.

- I also implement a high performance graph analytic library for realworld scale-free data, which leverages the techniques from the three previous contributions. For a broad class of problems this library also outperforms the state of the art.

### Chapter 2

### A Method for High Performance

### 2.1 Introduction

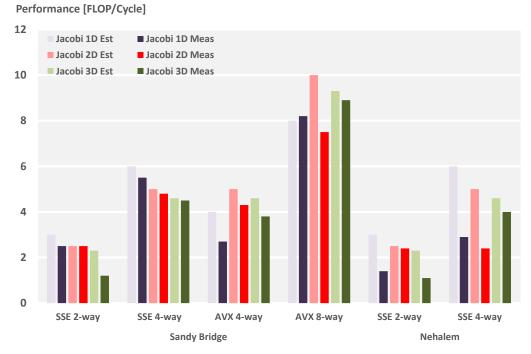

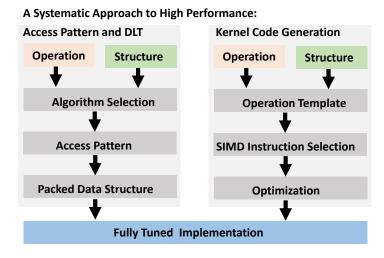

In this chapter, we describe the method for producing high performance implementations of matrix-like operations in the domains of dense linear algebra, structured mesh, sparse linear algebra and graph analytics. This two part method – illustrated in Figure 2.1 – obtains performance by first yielding an efficient access pattern, which can provide a high rate of access through the memory hierarchy (Figure 2.2 left) to the second component of this process – a generated kernel that is tuned to the system's microarchitecture (Figure 2.2 right) to maintain this rate of computation. This method is a generalization of the Goto approach [2] for designing high performance implementations of dense matrix-matrix multiplication. In order to make this generalization from the dense to sparse we take into account the structure of the data, in particular the relationship between the elements in the dataset and their neighbors. By taking a structure-centric approach, we reshape the dataset and build algorithms on them in such a way that we are no longer computing on sparse data, but instead on dense clusters. We then use the same techniques for generating high performance dense matrix-matrix multiply kernels for these dense clusters. Thus, finding and capturing this structure is key for this method.

To elaborate on this method for high performance (Figure 2.1), we begin with the operation, which is a mathematical that maps the input of the A Systematic Approach to High Performance:

Figure 2.1: Throughout this thesis we use this two part process to produce high performance implementations of matrix-like operations. This method divides the implementation of an operation into an efficient access pattern that feeds an efficient kernel that performs the computation. This process is a generalization of the Goto technique [2] for high performance Matrix-Matrix Multiplication.

problem to the desired output. We restrict ourselves to operations that are similar to matrix-matrix, matrix-vector and iterative matrix-vector multiplication. This restriction allows us perform our computations using a class of algorithms, divide-and-conquer, which are amenable to machines with deep cache hierarchies.

How we layer these divide-and-conquer algorithms depends entirely on the input dataset is partitioned, which is why we focus on structured (dense and structured mesh) and semi-structured (scale-free networks) data. This partitioning is determined by the structure of the data because we want to hierarchically capture the dense clusters of elements in the data. With this hierarchical partitioning we determine the layering – or nesting – of divideand-conquer algorithms that recursively compute on these partitions. We then pick a data structure that provides efficient access to the partitioned data. The dataset is then packed contiguously in this data structure, also prescribed by the algorithm nesting. These steps result in an efficient access pattern for a tuned computational. This kernel starts with the inner most nesting of algorithms from the previous step. We then select a mix of instruction to map this nesting of algorithms to the hardware. This mix is then statically scheduled and then optimized before being emitted as kernel code. We then combine the access pattern and kernel to produce the high performance implementation of the target operation.

We apply this approach in the remainder of thesis, where we target four domains using parts or the whole of this method. We selected these domains because they are representative of four of the computational dwarfs in [3] and span a large space of computational science. In Chapter 4, we automate this method by providing a systematic approach to generating expert level matrix-matrix multiply kernels. The data access portion of this process is provided by [2, 1]. In Chapter 5, we apply this method to structured mesh computations and we demonstrate how structure plays an important role in both the access pattern and in the kernel code. In Chapter 6, we demonstrate how to apply this entire method to sparse matrix operations on synthetic scale-free data which hinges on using the underlying structure in the data. We extend this to graph operations on real-world data in Chapter 7 to show that the necessary structure for this method does exist in real data. The remainder of this chapter is devoted to a detailed description of this method for high performance.

Figure 2.2: Our focus for performance is exclusively on the memory hierarchy and the microarchitecture. The method described in Figure 2.1 creates a high performance implementation by laying the dataset to efficiently feed a kernel tuned to the microarchitecture.

### 2.2 Preliminaries

In this section, we will provide a brief overview of the computational domains and the class of operations in these domains that we target. In particular, we will describe the linear algebra-like operations where this method for performance works. Lastly, this thesis focuses on obtaining high performance on modern computer architectures, therefore we will discuss the characteristics of these architectures.

#### 2.2.1 Domains

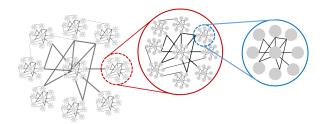

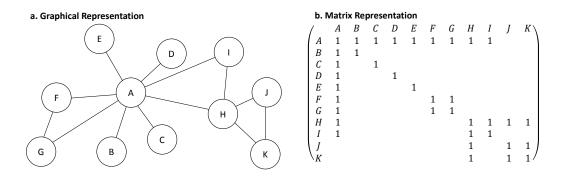

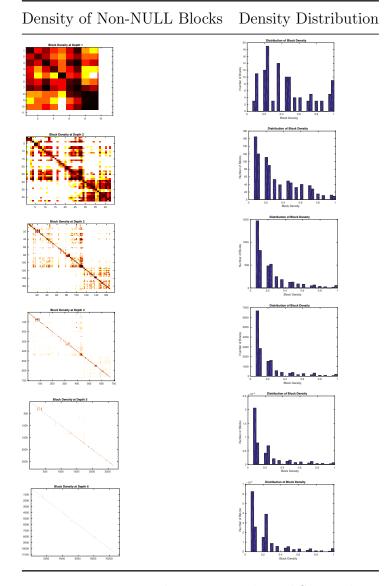

In Figure 2.3 we show a graphical representation along with its corresponding matrix representation of the data typically found in the four domains that we target. We picked these domains partly because they represent data typically seen in a large number of scientific applications. More importantly, we selected these domains because they present their own unique challenges in how data in these domains are structured.

**Dense Linear Algebra.** In this domain, datasets are dense because the value of an element is determined by a linear combination of all elements in the system. If we were to represent this graphically, this connectivity leads to a complete graph. This domain is at the heart of high performance computing to the extent that the performance of large machines are determined by the speed at which they can compute solutions to large dense systems of equations. Thus, modern computer architectures are typically optimized for these computations. We selected this domain because it provides the benchmark for our method.

Structured Mesh (Stencils). These computations typically arise in the computation of PDEs using finite-difference methods. The structure of this data is typically an n-dimensional mesh that corresponds to the relationship between an element and its neighbors. We chose this domain because exploiting this regular structure is critical for performance.

**Sparse Linear Algebra.** Data in this domains typically arises in the solution of PDEs using finite-element methods. The structure of this data is dependent on how the problem domain is divided into mesh elements. In

Figure 2.3: In this thesis we target four different domains: Dense Linear Algebra, Structured Mesh, Scale-Free and Real-World Networks. On the left we show a graphical representation of these domains with the matrix interpretation shown on the right. We picked these domains because they represent four of the original Seven Computational Dwarfs [3].

this thesis we actually restricted ourselves to sparse matrices generated from synthetic scale-free data. This data is fractal-like and hypersparse and fairly representative of real-world graph data. We chose this domain the show that the method for performance works on sparse scale-free data.

**Graph Analytics.** The data in this domain typical arises from biological and social networks. This data is typically scale-free, but random. A hallmark of this data is the hierarchical clustering of elements that naturally captures dense communities. This domain was selected to demonstrate that the method indeed works on real-world data.

### 2.2.2 Operations and Semirings

We restrict our method to matrix-like operations over the described domains. Specifically, these operations are matrix-matrix multiplication, matrix-vector multiplication and iterative matrix-vector multiplication which are described in Table 2.1. We say these are matrix-like operations because we define them over operation specific *semirings*. At a high level these semirings replace the addition and multiplication operator with a different function. More formally, a semiring is a set S with an additive operator + (which is not necessarily the standard addition) and a multiplicative operator × (once again, not necessarily the standard multiplication), along with an additive identity 0 where a + 0 = a and a multiplicative identity 1 where  $a \times 1 = a$ .

For example, if we want to compute Single Source Shortest Path (SSSP) as an iterative matrix-vector product, then we would formulate the semiring as follows: S is an integer value which corresponds to distance to the source, the additive operator + is the minimum value between two elements in S, the multiplicative operator  $\times$  is the addition of two elements from S, the additive identity is  $\infty$ , and the multiplicative identity is zero. In Table 2.2, we list the matrix operation and semiring for the operations discussed in this thesis. The author in [4] provides a listing of semiring-like operations for n-body problems and in [5] the authors describe graph operations in terms of semirings.

#### 2.2.3 An Overview of Modern Computer Architecture

We target modern computer architecture which are characterized by two key features, deep memory hierarchies and complex microarchitectures. This is

| Operation               | Matrix Form | Formalism                               |

|-------------------------|-------------|-----------------------------------------|

| Matrix-Matrix           | C = AB      | $c_{ij} = \sum_{p=1}^{k} a_{ip} b_{pj}$ |

| Matrix-Vector           | y = Ax      | $y_i = \sum_{j=1}^{n} A_{ij} x_j$       |

| Iterative Matrix-Vector | $y = A^t x$ | $y = (\prod^p A)x$                      |

Table 2.1: These are the matrix operations we target in this thesis. By defining these operations over arbitrary semirings we are able to target a large class of problems.

| Operation     | Matrix Op.  | +                          | ×               |

|---------------|-------------|----------------------------|-----------------|

| Matrix-Matrix | C = AB      | fadd(a,b)                  | fmul(a,b)       |

| Matrix-Vector | y = Ax      | fadd(a,b)                  | fmul(a,b)       |

| Stencils      | $y = A^t x$ | fadd(a,b)                  | fmul(a,b)       |

| SSSP          | $y = A^t x$ | min(a,b)                   | add(a,b)        |

| PageRank      | $y = A^t x$ | <pre>scaled_add(a,b)</pre> | dampen_add(a,b) |

Table 2.2: In this table we describe the operations treated in this thesis and how they are represented as matrix-like operations over arbitrary semirings.

Figure 2.4: Here we provide a representative overview of a modern shared memory architecture. We color code each icon as follows: orange represents a computational unit, blue represents a storage unit and green corresponds to a communication unit. Additionally, we show how these units are connected to each other. For example, in the socket level view, each core must pass through a common interconnect in order to reach the shared last level cache.

why we split our method into two parts, where the first part focuses on the memory hierarchy and the second part focuses on generating a tuned kernel for the microarchitecture. In Figure 2.4, we illustrate a modern computer architecture at multiple levels of granularity from the system level all the way down to a functional unit view. Note, in each of these views, we distinguish between compute, memory and communication units and how they interconnect.

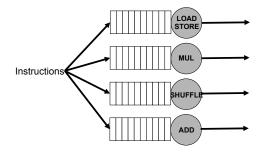

Figure 2.5: We can subdivide Figure 2.4 by exposing the view of a SIMD functional unit which compute short vector SIMD instructions. These functional units perform multiple independent operations simultaneously using a single instruction.

Continuing with the figure, we start at the system level which is composed of multiple compute sockets where each socket can directly access its own memory and can access the memory of its neighbors at the added cost of communicating over a shared bus. This configuration is called Non-Uniform Memory Access (NUMA). Second, we can decompose these sockets into multiple compute cores that communicate to each other over a shared On-Die Interconnect that connects to a shared Last Level Cache (LLC). This configuration, where each compute element shares access to the same memory at the same speed, is called Symmetric Multi Processor (SMP). Next, we can divide a core into Hardware Threads that share functional units that access the L1 and L2 cache. These hardware threads also share the underlying hardware resources on the core. We can view each thread as having its own private memory in the form of a register file, where computation on this register file is performed by a variety of Single Instruction Multiple Data (SIMD) functional units and communication between these units is governed by the instruction scheduler. These SIMD instructions compute short vector operations using a single instruction, and are necessary for performance on these architectures. We go even further in describing these SIMD functional units in Figure 2.5. Here each element in a SIMD functional unit corresponds to a location in a vector register. We have multiple scalar functional units which compute on specific locations in the SIMD vector and the communication of elements between these vectors is performed by the shuffle and permute engine. In Figure 2.2, we provide a simplified view of a modern architecture where we show the memory hierarchy and a combined view of the microarchitecture.

Given a computer architecture that fits this described model, performance is obtained by efficiently streaming the dataset through this hierarchy of memory and caches, and effectively using all of the computational units in parallel. In the next two sections, we will show how we target operations to this hierarchy and microarchitecture.

### 2.3 A Method for Efficient Data Access

We have a two part method for obtaining performance on modern computer architectures that splits the problem into efficient data access and kernel code generation. The goal of the first part of our method (labeled Part I in Figure 2.1) is to produce an efficient access pattern that brings the working dataset through the memory hierarchy as quickly as possible. This process entails dividing the original dataset in smaller working sets that can fit through the various levels of cache between DRAM and registers (left side of Figure 2.2). We achieve this by partitioning the dataset hierarchically in a manner that preserves tightly connected clusters. We then implement the target operation as layering of divide-and-conquer algorithms over the partitioned data which will move these partitions through the memory hierarchy in a cache efficient manner. Once we determine a layering of algorithms, we transform and repack the dataset to match how it is accessed. This insures that the kernel generated in the next section (labeled Part II in Figure 2.1) has contiguous access to the data. In the remainder of this section we will detail this process and in the next section we will connect this to the kernel generation.

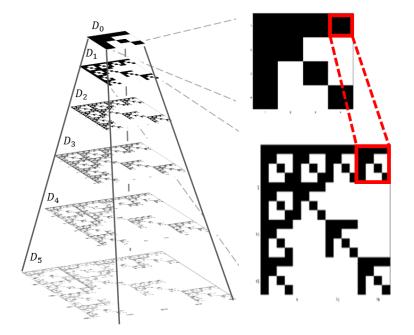

### 2.3.1 Partitioning the Data

Partitioning the dataset is critical for performance because the operations we target essentially compute an element's value based on its neighbors (for example PageRank). Thus, maintaining the physical locality of the dataset in how it is partitioned will maximize cache utilization of neighboring elements. In our approach, we recursively partition our dataset in a manner

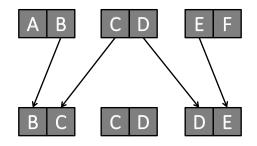

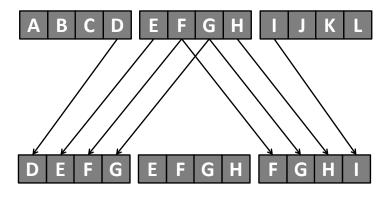

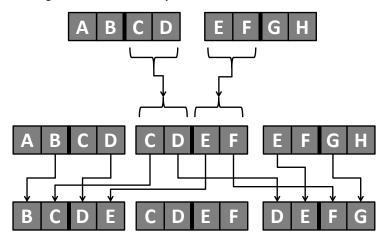

Figure 2.6: For each domain we show two different strategies for partitioning the data using only two partitions in the first two domains and three in the last two. How we partition our data will greatly affect the performance of the computations being performed on them. Ideally, we want partitions to capture clusters of neighboring data.

that hierarchically captures compute dense communities in the data. This allows us to efficiently map the dataset to memory using divide-and-conquer algorithms. These algorithms work by recursively traversing through this hierarchical partitioning until a small enough partitioned is reached an computed on. By computing an entire partition before proceeding to the next makes these algorithms amenable to the cache hierarchy. However, in order to effectively use the cache these partitions need to fit the cache which they are targeting and ideally these partitions contain elements which communicate frequently with each other.

In Figure 2.6, we show two different partitionings for our four dataset examples. In the case of our Complete Graph (representative of DLA) both partitionings are equally as good because each partition contains an equal number of elements and these elements have the same number of edges between them. In the Structured Grid example, we preference the partitioning which keeps neighboring grid elements together because these grid points exchange information to each other, thus keeping them in the same partition insures that this information is exchanged more frequently than if they were not in the same partition. This is more apparent in the Scale-Free and Real-World examples where one set of partitions captures the community clusters and the other does not.

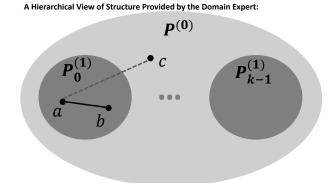

More formally, we can state a hierarchical partitioning over graph G = (V, E) as follows: First, let the top level partition be  $P^{(0)} = V$ , then we can partition the vertices such that all partitions for a given level *i* cover their parent set,  $P^{(i)} = \bigcup_j P_j^{(i+1)}$ , and these partitions are non-overlapping,  $\emptyset = \bigcap_j P_j^{(i+1)}$ . If we want each partition at a particular level *i* to fit in a given cache of size *s*, then we would select are partitions such that  $\forall_j |P^{(i)}| \leq s$ . We can express this constraint for each level of the memory hierarchy.

Now, it is critical that we select our partitions in a way that captures tightly connected clusters. The elements in these cluster communicate more with each other than elements outside of their community. To express this, we need a graphical view our partitions, let  $G_{jk}^{(i)} = (V_{jk}^{(i)}, E_{jk}^{(i)})$  which is the subgraph that connects vertices of  $P_j^{(i)}$  to vertices of  $P_k^{(i)}$  where  $V_{jk}^{(i)} = V \cap (P_j^{(i)} \cup P_k^{(i)})$  and  $E_{jk}^{(i)} = E \cap (P_j^{(i)} \times P_k^{(i)}))$ . To express our goal that the partitions capture dense communities we can use the following formulation:  $\forall_j | E_{jj}^{(i)} | \geq \sum_{k \neq j} | E_{jk}^{(i)} | + | E_{kj}^{(i)} |$ . This states that we want the number of edges within the graph of a partition to be greater than the number of edges leaving that partition. Capturing these communities is the objective of partitioning,

however it is up to the expert to determine these partitions within these constraints. If they do satisfy these constraints then the following steps in this section will insure to production of a high performance data access pattern.

The expert can use a graph partitioner to automatically determine these partitions [6]. However, this approach is computationally expensive. Ideally, this partitioning step is performed by the domain expert prior to the computation. The expert is typically involved in the collection of the dataset therefore the expert can use her domain knowledge at this step to determine the location of these partitions.

For the purposes of this chapter, we will assume that these partitions are obtained and stored hierarchically. We will also assume that this partitioned data is stored in a way which we can access the partitions. In the following code listing, we illustrate how a partition  $G_{jk}$  from the graph G:

```

G_jk = get_col_part( get_row_part( G, j ), k )

```

In this code snippet, obtaining the incoming edges into subgraph corresponds to gathering the column partitions of an adjacency matrix, and obtaining the outgoing edges corresponds to gathering the row partitions. Combining these two functions allow us to extract subgraphs from a larger graph. We will express our divide-and-conquer algorithms in terms of these extractions. If our partitions capture physically locality, then these algorithms will preserve them throughout the cache hierarchy.

### 2.3.2 A Nesting of Algorithms

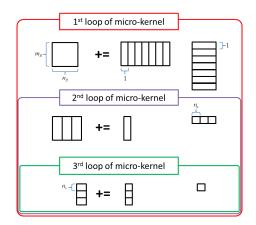

In this section we show how a nesting of divide-and-conquer algorithms efficiently computes on the partitions of the previous subsection. These algorithms recursively divide the dataset until a base case is reached and directly computed on. For our purposes, the size and contents of these divisions is determined by the partitioning of the dataset. Thus by hierarchically capturing clusters, we can insure that computations within a cluster occur before computations outside said cluster, and this computation occurs within the cache.

If we continuing with our running matrix-vector and use the dataset and partitioning in Figure 2.6, then we can decompose it into the following nesting of algorithms:

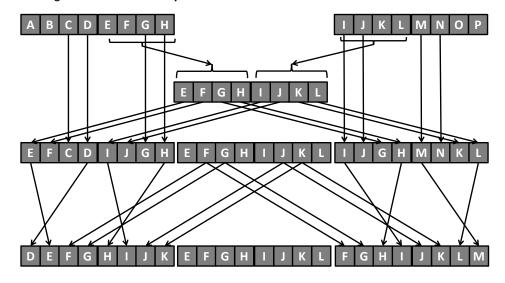

Figure 2.7: **Top:** we show the partitioning of the output vector y and the input vector x. **Bottom:** We show the application of divide-and-conquer algorithms to performance matrix-vector multiplication (y = Ax).

```

mv-row(y,A,x,

mv-col(_,_,_,

mv-row(_,_,_,

mv-col(_,_,_,

op(_,_,_ )))))

```

Here we perform the computation by alternating between an algorithm that computes by rows and one that computes by columns using the algorithms from Table 2.3. How the algorithms decompose the dataset is based on its partitioning (Figure 2.6). We illustrate this pictorially in Figure 2.7. Alternatively, we can express this nesting as the following series of C loops:

We can clearly see that in the first two loops we divide the problem into sixteen  $2 \times 2$  matrix-vector multiplies and the second set of loops computes those  $2 \times 2$  multiplies. Additionally, note that indexing (idx\_A, idx\_y and idx\_x) is described as a function of the loop variables. This is done to separate the logical indexing of the data from the physical indexing in memory. Ideally, this mapping is designed to insure contiguous memory access.

In Table 2.3, we show the algorithms we use for Matrix-Vector Multiplication, Iterative Matrix-Vector Multiplication and Matrix-Matrix Multiplication. We call the recursive application of these algorithms a *nesting* and this determines how the dataset is accessed during the computation. Ideally, we want the elements in the dataset stored in the order that they will be computed, so we will take this a step further in the next subsection use this nesting to rearrange the dataset in that desired order.

**Coarse Grain Parallelism.** As we indicated in Figure 2.4, modern systems provide various resources for coarse grain parallelism. We determine the division of computation across these resources through the selection of the same algorithms which have been decorated with parallel directives.

| Algorithm                     | Formula                      | Code                                                                                                                           |

|-------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| mv-row(y,A,x,op)              | $y_i = A_{i:x}$              | <pre>for(i=0;i<nrows;i++) a_i="get_row_part(A,i)" op(y_i,a_i,x)<="" pre="" y_i="get_row_part(y,i)"></nrows;i++)></pre>         |

| mv-col(y,A,x,op)              | $y = A_{:j} x_j$             | <pre>for(j=0;j<ncols;j++) a_j="get_col_part(A,j)" op(y,a_j,x_j)<="" pre="" y_j="get_col_part(x,j)"></ncols;j++)></pre>         |

| <pre>imv-it(y,A,x,T,op)</pre> | $y = A^T x$                  | <pre>r[0] = x for(t=0;t<t;t++) op(r[t+1],a,r[t])="" y="r[T]&lt;/pre"></t;t++)></pre>                                           |

| mm-row(C,A,B,op)              | $C_{i:} = A_{i:}B$           | <pre>for(i=0;i<nrows;i++) a_i="get_row_part(A,i)" a_i,="" b)<="" c_i="get_row_part(C,i)" op(c_i,="" pre=""></nrows;i++)></pre> |

| mm-col(C,A,B,op)              | $C_{:j} = AB_{:j}$           | <pre>for(j=0;i<ncols;j++) a,="" b_j="get_col_part(B,j)" b_j)<="" c_j="get_col_part(C,j)" op(c_j,="" pre=""></ncols;j++)></pre> |

| mm-acc(C,A,B,op)              | $C = \sum_{p} A_{:p} B_{p:}$ | <pre>for(p=0;p<ncom;p++) a_p="get_col_part(A,p)" a_p,="" b_p="get_row_part(B,p)" b_p)<="" op(c,="" pre=""></ncom;p++)></pre>   |

Table 2.3: In this table we list the various divide-and-conquer algorithms used throughout this thesis.

The cost of communication and availability of the shared resources ultimately determine which algorithms get selected. For example, we preference partitioning by rows rather than columns because the latter requires accumulating to a shared resource (elements of vector y). This contention in turn requires locks which serialize access and potentially slow down computation if this access is in slower memory. Additionally, parallelism is not restricted to one level of the machine hierarchy. For example the authors in [7] provide a detailed treatment of nested parallelism.

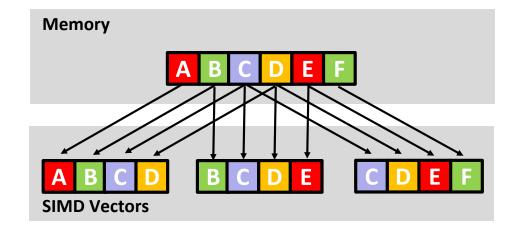

Fine Grain Parallelism. In Figure 2.5 we illustrate a Single Instruction Multiple Data (SIMD) functional unit. These instructions allow fine grain parallelism at the microarchitectural level. In order to use them, we have to design our code to efficiently use these instructions. Thus, our inner-most algorithms are typically selected to permit the computation of multiple independent operations because communication is typically expensive within a SIMD vector. Using matrix-vector multiplication as our example, we preference the algorithm by rows over the columns for the inner most algorithm because it computes multiple independent operations that accumulate to different values of the output vector y.

### 2.3.3 Designing a Data Structure

The algorithm nesting in the previous subsection tells us how the dataset is accessed logically (as a mathematical object) but it does not prescribe how the dataset will be accessed physically (as elements in memory). However, how the dataset is stored physically and the format in which it is stored will greatly impact the overall performance of the implementation. This is because our divide-and-conquer algorithms make extensive use of partition access (i.e. get\_row\_part and get\_col\_part). If we have a hierarchically partitioned graph like Figure 2.6, then we want a data structure that insures low cost access to these partitions. To achieve this, we will select a hierarchical data structure the matches our algorithm nest and the format for each level of that data structure is determined by the structure of the original dataset. In Chapter 6 and Chapter 7, we will show how we select a data structure for scale-free and real-world datasets.

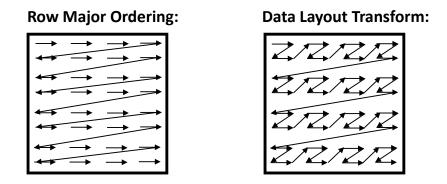

Figure 2.8: On the left we show a row major access pattern for a matrix and on the right we show the access pattern for our matrix-vector example. Ideally we want to arrange the matrix in memory in the access pattern on the right.

#### 2.3.4 The Power of a Data Layout Transformation

Once the algorithm nesting is determined, we can go one step further by insuring that the dataset is access in unit stride. Doing this will maximize our cache utilization and reduce the number of TLB entries needed to address the working data set [2]. For example, a standard two dimensional C matrix is most efficiently accessed in row major ordering (Figure 2.8 left) however, our matrix-vector example uses a more complex access pattern (Figure 2.8 right). Continuing with matrix-vector example, we can repack the input dataset A into A\_dlt where each element is stored in the other that it will be accessed:

```

p=0;

for(io=0 < 8; io+=2)

for(jo=0 < 8; jo+=2)

for(ii=0 < 2; ii++)

for(ji=0 < 2; ji++)

A_DLT[p++] =

A[idx_a(io,ii,jo,ji)];

```

Once our data is repacked, we can implement our algorithm nesting using A\_dlt:

We can see that each element of A\_dlt is accessed in the contiguous order illustrated on the right side of Figure 2.8. By performing this repacking, we can insure that the kernel we generate will efficiently access the dataset.

# 2.4 A Method for Fast Kernels

In the previous section, we outlined the process for constructing on efficient access pattern for matrix-like operations. In this section we discuss the second part of our method – how to construct an efficient kernel for this access pattern. We do this by extract the inner most loops of our access pattern which we will call the kernel. Using our matrix-vector multiply example we would separate the outer two loops from the inner two loops to form the access pattern and kernel:

Then, we find an efficient mix of instructions that implements this kernel. After that, we statically schedule these instructions. Last, we optimize and emit these instructions as code. In the rest of this section we detail our generic process for generating kernels.

#### 2.4.1 Selecting an Instruction Mapping

In Figure 2.5 we illustrate a SIMD functional unit and in order to produce a high performance implementation we need to efficiently utilize these units. Given a kernel we can find a myriad of instruction mixes – or combinations of SIMD instructions – that implement the kernel. Continuing with our  $2 \times 2$  matrix-vector multiplication kernel, we can construct two different instructions mixes for the same operation. In this first example, we store the y vector in a SIMD register and broadcast each element of x into their own register. We will call this the broadcast-based instruction mix.

```

x0vec = vbroadcast(x[0])

x1vec = vbroadcast(x[1])

A0vec = vload(A[:][0])

A1vec = vload(A[:][1])

r0vec = vfma(A0vec, x0vec, 0)

r1vec = vfma(A1vec, x1vec, r0vec)

vstore(y,r1vec)

```

In the next example, we load rows of A into SIMD registers that are multiplied by a SIMD register of x elements, and the resulting vectors are accumulated within the register and stored into y. We will call this the accumulation-based instruction mix.

```

xvec = vload(x)

A0vec = vload(A[0][:])

A1vec = vload(A[1][:])

r0vec = vmul( A0vec, xvec )

r1vec = vmul( A1vec, xvec )

y0sca = hadd( r0vec )

y1sca = hadd( r1vec )

sstore( y[0], y0sca )

sstore( y[1], y1sca )

```

Both of these instruction mixes will implement the desired matrix-vector kernel. However, we want to select the most efficient kernel. In particular we want to select a mix that sustains a high rate of computation because many of these kernel operations will be performed inside a nesting of loops. In this situation, the individual performance of a kernel is less important than the steady-state performance.

Selecting a High-Throughput Instruction Mix. Our goal is to find the instruction mix that, on average, takes the fewest number of cycles to pass through the microarchitecture. Because we are only interested in the instruction mix performance inside a much larger loop in steady-state, we can use Little's Law [8] to model the microarchitecture. Little's law tells us that the average waiting time of a queue in steady-state, W, is equal to the average number of elements in the system N divided by the average arrival rate of elements into the system,  $\lambda$ . We can express this as follows:

$$W = \frac{N}{\lambda} \tag{2.1}$$

Because the system is in steady-state, the arrival rate of elements into the system is equal to the average departure rate out of the system. We can use this formula to estimate the average amount of time it takes the microarchitecture to clear a given instruction mix in steady-state. We are not concerned if those instructions came from the same iteration, but rather we want to know if that particular mix of instructions has moved through the processor, this allows us to ignore instruction dependencies for this computation.

To illustrate this, let us assume that we only have one type of functional unit that computes at a rate of two instructions per cycle ( $\lambda = 2$ ), and let us select the broadcast based matrix-vector multiply instruction mix from the beginning of this subsection which has N = 7 instructions. By modeling this system as a queue we can apply Little's Law, so the average waiting time of the instructions in this mix would then be 3.5 cycles.

However, if we want to model a more complex microarchitecture, then we can adjust our calculations. If we have multiple functional units, then we are concerned with the functional unit that is the bottleneck. We want to know which functional unit, queue, has the longest average waiting time. For example, let us assume that we have two functional units, a memory functional unit and a arithmetic functional unit. We assign them their own average waiting time  $W_{\text{mem}}$  and  $W_{alu}$ , and their own average arrival rate  $\lambda_{\text{mem}}$ and  $\lambda_{alu}$ . Let us also assume that our microarchitecture has two memory functional units and one arithmetic functional unit, that will give us  $\lambda_{\text{mem}} = 2$ and  $\lambda_{alu} = 1$ . If we take the broadcast based matrix-vector kernel, we can divide its instructions into two queues with  $N_{\text{mem}} = 5$  and  $N_{alu} = 2$ . This would result in the waiting times of  $W_{\text{mem}} = 2.5$  and  $W_{alu} = 2$ . This means that on this microarchitecture the broadcast based implementation has a waiting time of 2.5 cycles. We can apply the exact same process to the second instruction mix, the accumulation-based mix, for the matrix-vector kernel, where we have  $N_{\text{mem}} = 5$  and  $N_{alu} = 4$ . This mix will give us a maximum average waiting time of 4 cycles. Thus, for this hypothetical architecture, the first instruction-mix will sustain a higher throughput relative to the second one. This process only estimates which mix will have the lowest waiting time on average in the steady-state. Once we select this mix, we will need to schedule the instructions in order to sustain the estimated performance.

#### 2.4.2 Instruction Scheduling is Important

Once an instruction mix is selected, we need to statically schedule the instructions in order to sustain the rate of computation enabled by the mix. Typically, instruction take more than a single cycle to compute, and if we do not overlap instructions then during those cycles the processor is stalled. Thus, we prevent these stall cycles by overlapping independent instructions during those stalled cycles. While most modern architectures are out-oforder, meaning they can rearrange instruction on the fly as resources become available, we show in [9] that at high throughput an out-of-order processor benefits from statically scheduled instructions. For our purposes, we use software pipeline scheduling [10] which is a systematic method for scheduling loops by interleaving instructions between different iterations in order to hide instruction latency.

#### 2.4.3 Further Optimizations and Code Generation

The last step of kernel generation process involves performing compiler optimizations on our scheduled instruction mix. For example, we fully unrolling the loops in the kernel which eliminates branching and simplifies index computation. Additionally, we include transformations such as common subexpression and array scalarization where arrays are replaced with scalar registers. Lastly, in Chapter 6 we show how we can specialize kernels to specific patterns and shapes that appear in the dataset. Once the code is optimized we generate it using ANSI C with inline assembly intrinsics that preserve instruction order. We detail this in [9].

# 2.5 Chapter Summary

In this chapter, we outlined our two part method for producing high performance implementations of matrix-like operations. This process is a generalization of the Goto approach for matrix-matrix multiplication, and works by yielding an efficient access pattern that feeds a tuned kernel. We also detailed how we use problem structure to generalize this approach to domains outside of dense linear algebra, specifically to operations that are expressible as matrix-like operations over arbitrary semirings. In the following chapters we will highlight key features in this method and show that it is extensible to various domains such as structured mesh computations, sparse computations and graph analytics.

# Chapter 3

# **Related Work**

# 3.1 Introduction

In this chapter, we describe the overarching story of the development of high performance computational libraries for the domains targeted in this thesis. We will also show how these domains relate to one another and lay the groundwork for our approach. Additionally, we will discuss where this thesis fits in this story.

Before beginning, we will provide a brief overview of what follows. We will start with the development of high performance Dense Linear Algebra (DLA) libraries. The advances in this field proceeded in lock step with the development of computer hardware, responding to the divergence in processor and main memory speed, then the advancement of caches and eventually with the addition of short vector instructions. These refinements have led to the development of modern Linear Algebra libraries that cast the bulk of their work in terms of the Matrix-Matrix Multiplication operation, which in turn is built on divide and conquer algorithms that partition their inputs into cache size blocks that are eventually computed on hand tuned kernels. Thus the bulk of DLA performance rests on the shoulders of expert coders who hand tune Matrix-Matrix Multiply kernels. In this thesis we provide a systematic approach to generating these kernels.

While the machinery for DLA achieves high performance, it is not necessarily suited to problems over structured matrices such as those which arise from solving differential equations over discretized objects, i.e. when *Finite Difference Methods* are employed. In this domain, the very regular structure the arises from discretization of physical objects is exploited in the selection and implementation of algorithms for solving these problems. What results is a layering of loops – which partition the problem in both spacial dimensions and in the temporal dimension – over a kernel which acts as a *stencil* over these discretized points. Like Matrix-Matrix Multiply kernels we also provide a mechanical approach to generating high performance stencil kernels.

The previous two domains deal with extremely regular problems. However, half of this thesis targets graph analytics over seemingly unstructured real-world problems. To bridge the previous work to the graph domain, we discuss the work done by Kim et. al. in [11] where they show that high performance for *Finite Element Methods* (FEM) is achievable without graph partitioning. They do this by retaining the structural information of the input domain and using this to determine how elements are stored in a hierarchical data structure. In this thesis, we leverage this idea for real-world graphs with underlying structure.

The current state of the graph domain can be captured in two different approaches. The first is a dataflow approach which expresses graph operations as functions over edges and vertices that are applied when their inputs are modified an continue until a convergence criteria is met. Overhead is the limiting factor in this approach. The second approach, cast graph operations in terms of Linear Algebra over operation specific semirings. Much like DLA, in this approach performance is dependent on the underlying building blocks which we will address in this thesis.

### 3.2 Related Work

In this section, we elaborate on the historical development of Matrix-Matrix Multiplication, Stencil computations, Sparse Matrix computations and graph analytics.

Matrix-Matrix Multiplication. In the field of Dense Linear Algebra (DLA), Matrix Multiplication is the key operation on which most of the BLAS-3 [12] and LAPACK routines [13]) are built [14, 15].

As long as this operation is efficient on a given target architecture, then all other BLAS-3 and LAPACK operations that cast the bulk of their computation on it could leverage this performance. It was recognized that one could achieve high performance for matrix-matrix multiplication by taking advantage of its high operational intensity and exploiting algorithmic optimizations such as blocking to achieve a high level of performance.

In PhiPAC [16], the authors took this blocked approach and parameterized the various optimizations over the operations so search – or auto-tuning – could determine their values. This auto-tuning approach was extended by ATLAS [17] which decoupled the compute kernel from the bulk of the data access by packing the working data-set into buffers for a tuned kernel to compute on. The authors of [18] identified that many of the search parameters can be determined analytically without search.

The GotoBLAS [2] provided a key insight regarding blocking that if the blocking strategy can guarantee that the working data-set can be brought to the registers at the rate necessary for peak performance then given an efficient kernel peak performance can be practically achieved. The authors further identified that blocking for the L2 cache is sufficient on modern machines and that performing a data layout transformation simplifies the construction of a high performance kernel. The BLIS [19] project extended the Goto-BLAS by decomposing via blocking into an even smaller micro-kernel. Once the outer blocking parameters are determined [20] tuning this kernel to a given architecture is all that is necessary for high performance. In [21], we automate this last leg of performance for Matrix-Multiplication by distilling the kernel down even further and automating its generation. In this thesis, we discuss how we generate these high performance kernels.

It is worth noting that a great deal of work has focused on the generation of cache resident small matrix kernels such as LGen [22, 23, 24] and the Built-to-Order BLAS [25]. For many scientific and engineering application there is a need for linear algebra operations on cache resident data which these kernel code generators solve. However our focus is on problems larger than the cache.

Stencils and Structured Mesh. Many applications, which can be expressed in terms of Linear Algebra, give rise to systems of equations with very specific structures. For example in solving Partial Differential Equations (PDE) using Finite Difference Methods (FDM) the resulting system of equations for a 3 dimensional object can be expressed using a tridiagonal matrix. This type of matrix is far from dense which makes DLA libraries inefficient for solving these systems of equations. These problems are extremely regular and can be expressed as the successive application of function over

every point, where the function computes the value of each point from its neighbors.

This function is called a *Stencil* because it applies a repeated pattern over a collection of elements. Stencil Computations are not restricted to PDEs, in fact they appear in convolution codes in signal and image processing, in simulations for cellular automata, weather and earthquakes and in any domain where the computation can be described as a regular computation over neighboring elements. Because of their ubiquity and importance in scientific computing, the compiler community has focused a great deal of attention on optimizing them.

In the early 1980s compilers were designed specifically for compiling stencil kernels like the [26, 27, 28]. These early compilers split the stencil computation into two parts: A microcode compute kernel, which was fed to the sequencer of the Connection Machine, and a layering of outer loops that dealt with data movement which fed the appropriate elements to the kernel. These stencil compilers achieved performance by focus on the reuse of elements across multiple stencils (multistencils) and minimizing communication across nodes.

As caches became more common, new stencil designs focused on the explicit use of cache locality through tiling. The authors in [29] identified that explicit cache tiling is not necessary for one and two dimensional stencils because even a small cache is sufficient for reuse. However, as the number of dimensions increase, explicit cache tiling becomes necessary for performance. In their work the provide a strategy for applying tiling to three dimensional stencil codes, along with an analytical approach to determining tile sizes. In [30] the authors identify the limitations of spacial tiling alone and provide strategies for prefetching using a model based approach.

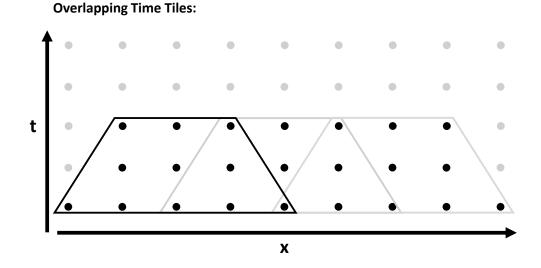

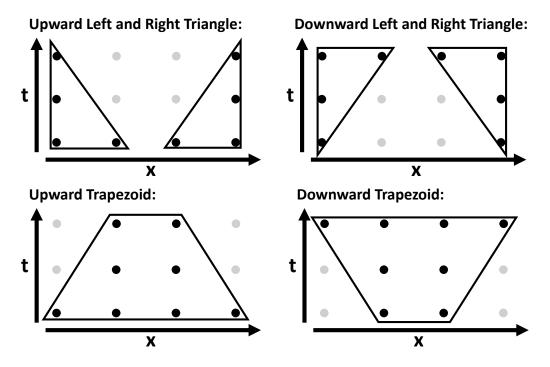

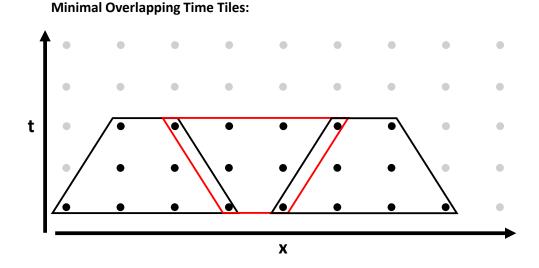

The issue is that only blocking in the spacial dimensions of a stencil ignores the amount of reuse that can be obtained by also blocking in the time dimension. In the paper [31], the authors identified that loop skewing alone is not sufficient to improve locality in stencils, but when combined with loop interchange and data forwarding it becomes a more powerful transformation called *time skewing* or *time tiling*. The idea is that the stencil dimensions can be rearranged to allow for blocking in the time dimension. This is made more powerful by forwarding the result of one iteration to the next, without making a round trip to memory. This approach is automated in the Panorama compiler [32] for a broad class of imperfectly nested stencil problems. In [33] the authors extend time tiling to modern multiprocessors with deep memory hierarchies. In their treatment of time tiling they provide a systematic approach for determining tile sizes.

In [34] the authors put these techniques to practice and develop a temporal blocking stencil implementation for the Gauss-Seidel algorithm for multigrid solvers. The idea is that cache sized multistencils are applied iteratively over the same block before proceeding to the next block. This insures that the computation of the multistencil occurs entirely within cache after the first iteration, as opposed to being loaded from main memory before each iteration. This is significant development in stencil computations because now stencil performance is no longer dependent on the bandwidth between main memory and the processor, but on the size of the cache and the ability of an expert programmer to produce an efficient kernel.