# Silicon Oxide is a Non-Innocent Surface for Molecular Electronics and

## Nanoelectronics Studies—Supporting Information

Jun Yao,<sup>1</sup> Lin Zhong,<sup>\*2,3</sup> Douglas Natelson,<sup>\*3,4</sup> and James M. Tour<sup>\*2,5</sup> <sup>1</sup>Applied Physics Program through the Department of Bioengineering; <sup>2</sup>Department of Computer Science; <sup>3</sup>Department of Electrical and Computer Engineering; <sup>4</sup>Department of Physics and Astronomy; <sup>5</sup>Department of Chemistry, Rice University, 6100 Main St., Houston, Texas 77005 \*Email addresses: <u>lzhong@rice.edu</u>; <u>natelson@rice.edu</u>; <u>tour@rice.edu</u>

#### **Table of Contents**

Material Preparations, page S1 Figure S1, Electroforming processes in vertical polySi-SiO<sub>x</sub>-polySi, page S1 Figure S2, Resistive-switching *IV* curves in an amorphous-carbon-coated vertical polySi-SiO<sub>x</sub>-polySi device, page S2

### **Material Preparations**:

**polySi-SiO<sub>x</sub>-polySi**: The SiO<sub>x</sub> ( $x \sim 2$ ) layer was grown by plasma enhanced chemical vapor deposition (PECVD) at 650 °C using tetraethyl orthosilicate (TEOS) as a precursor. The flow rates of TEOS and N<sub>2</sub> were 55 and 210 sccm, respectively. The growth was done at a pressure of 600 mTorr with a growth rate at ~ 2 nm per min. The polySi layers (70 nm) were grown by PECVD and implanted with boron ( $7 \times 10^{15}$  cm<sup>-2</sup> at 5 KeV).

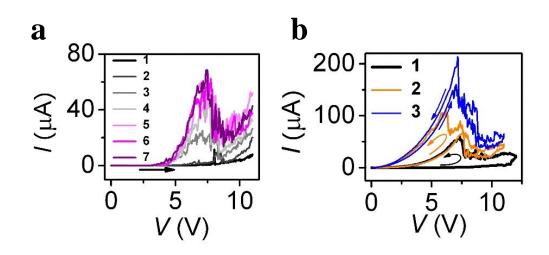

**Figure S1**. Electroforming processes in vertical polySi-SiO<sub>x</sub>-polySi (70 nm-10 nm-70 nm) devices by different sweep modes. The devices have the same structure and parameters as illustrated in the main article in Fig. 1c. (a) An electroforming process by consecutive forward voltage sweeps (0 V  $\rightarrow$  +11 V). Since each voltage sweep ends in the reset region, the formed device is always in an OFF state. (b) An electroforming process by consecutive loop voltage sweeps (0 V  $\rightarrow$  +12 V  $\rightarrow$  0 V). Since each voltage sweep finally bypasses the set region, the formed device is always in an OFF state. The arrows indicate the voltage-sweep directions and the numbers indicate the voltage-sweep orders. An electroforming process by consecutive backward voltage sweeps (e.g., +12 V $\rightarrow$  0 V) is similar to that described in Fig. 1b in the main article.

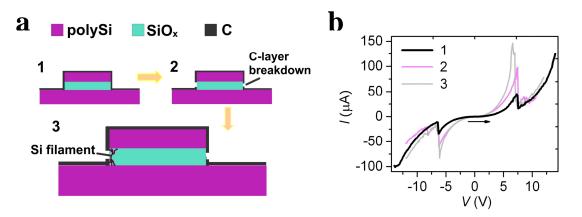

**Figure S2**. Resistive-switching *IV* curves in a vertical polySi-SiO<sub>x</sub>-polySi (70 nm-10 nm-70 nm) device coated with 5 nm-thick amorphous carbon. (a). Schematics showing the C layer assists the electroforming in the SiO<sub>x</sub> layer. 1. The initial C-coated structure. 2. Electrical breakdown in the C layer creates disruptions at the vertical SiO<sub>x</sub> edge. 3. The disruption in the C layer enhances the local filed and induces soft breakdown at the vertical SiO<sub>x</sub> edge. An electroforming process is then initialized with the formation of Si-

NC filament. (b). The electroforming process in an actual C-coated device. The arrow indicates the voltage-sweep direction and the numbers indicate the voltage-sweep orders. This is analogous to switching behavior observed in related systems.<sup>1-3</sup>

## References

- Yao, J.; Zhong, L.; Zhang, Z.; He, T.; Jin, Z.; Wheeler, P. J.; Natelson, D.; Tour, J. M. Small 2009, 5 2910-2915.

- 2. Li, Y.; Sinitskii, A.; Tour, J. M. Nat. Mater. 2008, 7, 966-971.

- 3. Sinitskii, A.; Tour, J. M. ACS Nano 2009, 3, 2760-2766.