# **Supporting Information**

# Theoretical Study of Triboelectric-Potential Gated/Driven Metal-Oxide-Semiconductor Field-Effect-Transistor

Wenbo Peng,<sup> $\dagger, \ddagger, \#$ </sup> Ruomeng Yu,<sup> $\dagger, \#$ </sup> Yongning He,<sup> $\ddagger$ </sup> and Zhong Lin Wang<sup> $\dagger, \$, *$ </sup>

<sup>†</sup>School of Materials Science and Engineering, Georgia Institute of Technology, Atlanta, Georgia,

30332-0245, USA

<sup>‡</sup>School of Electronic and Information Engineering, Xi'an Jiaotong University, Xi'an, 710049, China

<sup>§</sup>Beijing Institute of Nanoenergy and Nanosystems, Chinese Academy of Sciences, Beijing, 100083,

China

\*Email: zhong.wang@mse.gatech.edu

<sup>#</sup>These authors contributed equally to this work

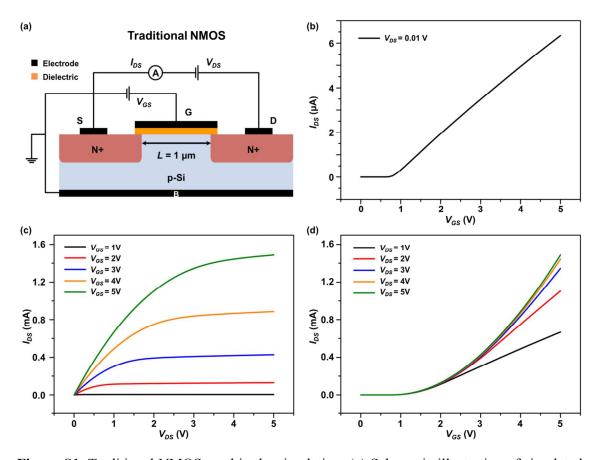

Figure S1. Traditional NMOS used in the simulation. (a) Schematic illustration of simulated traditional NMOS. (b-d) *I-V* characteristics of the traditional NMOS.  $I_{DS}$ - $V_{DS}$  characteristic with a small  $V_{DS}$  bias of 0.01 V indicates the threshold voltage is 0.8 V.

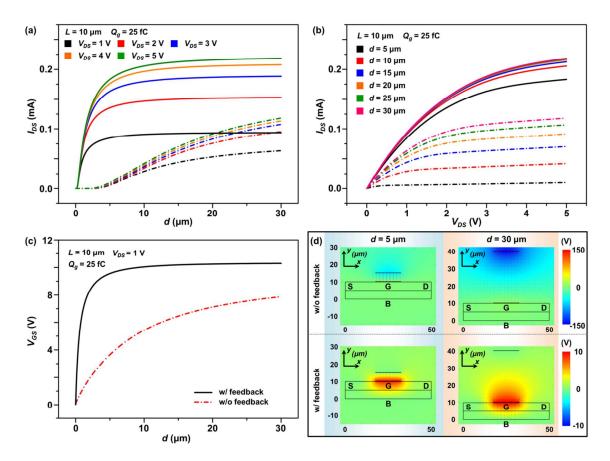

**Figure S2.** TPG NMOS with conduction channel length *L* of 10  $\mu$ m and *Q<sub>g</sub>* of 25 fC. (a) *I<sub>DS</sub>-d* characteristic with different *V<sub>DS</sub>* varying from 1 to 5 V. (b) *I<sub>DS</sub>-V<sub>DS</sub>* characteristic with different *d* varying from 5 to 30  $\mu$ m. (c) *V<sub>GS</sub>-d* characteristic with *V<sub>DS</sub>* of 1 V. (d) Electric potential and electric field distribution with *V<sub>DS</sub>* of 1 V under different d values: 5 and 30  $\mu$ m.

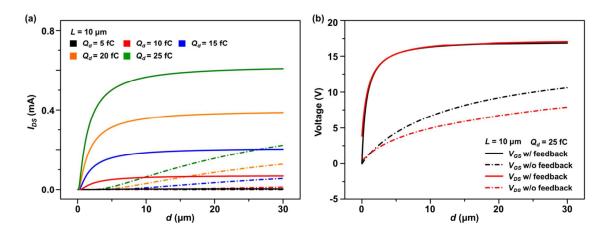

**Figure S3.** TPD NMOS with conduction channel length *L* of 10  $\mu$ m. (a) *I*<sub>DS</sub>-*d* characteristic with different *Q*<sub>d</sub> varying from 5 to 25 fC. (b) *V*<sub>GS</sub>/*V*<sub>DS</sub>-*d* characteristics with *Q*<sub>d</sub> of 25 fC.

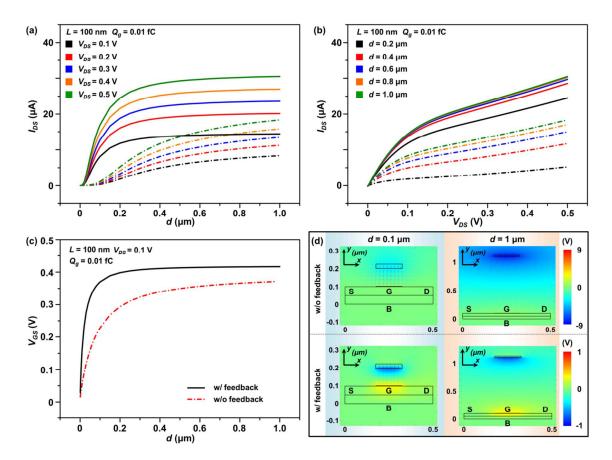

**Figure S4.** TPG NMOS with conduction channel length *L* of 100 nm and  $Q_g$  of 0.01 fC. (a)  $I_{DS}$ -*d* characteristic with different  $V_{DS}$  varying from 0.1 to 0.5 V. (b)  $I_{DS}$ - $V_{DS}$  characteristic with different *d* varying from 0.2 to 1.0 µm. (c)  $V_{GS}$ -*d* characteristic with  $V_{DS}$  of 0.1 V. (d) Electric potential and electric field distribution with  $V_{DS}$  of 0.1 V under different d values: 0.1 and 1 µm.

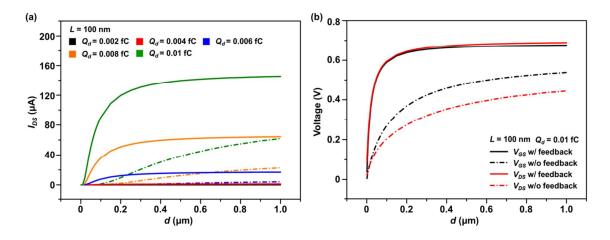

**Figure S5.** TPD NMOS with conduction channel length *L* of 100 nm. (a)  $I_{DS}$ -*d* characteristic with different  $Q_d$  varying from 0.002 to 0.01 fC. (b)  $V_{GS}/V_{DS}$ -*d* characteristics with  $Q_d$  of 0.01 fC.

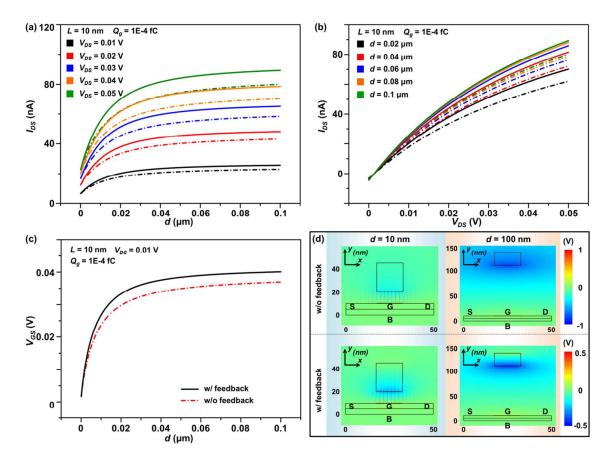

**Figure S6.** TPG NMOS with conduction channel length *L* of 10 nm and  $Q_g$  of 1E-4 fC. (a)  $I_{DS}$ -*d* characteristic with different  $V_{DS}$  varying from 0.01 to 0.05 V. (b)  $I_{DS}$ - $V_{DS}$  characteristic with different *d* varying from 0.02 to 0.1 µm. (c)  $V_{GS}$ -*d* characteristic with  $V_{DS}$  of 0.01 V. (d) Electric potential and electric field distribution with  $V_{DS}$  of 0.01 V under different d values: 10 and 100 nm.

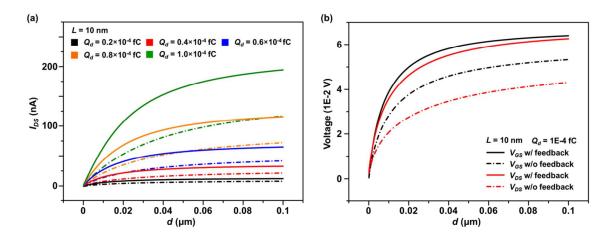

**Figure S7.** TPD NMOS with conduction channel length *L* of 10 nm. (a)  $I_{DS}$ -*d* characteristic with different  $Q_d$  varying from 0.2E-4 to 1.0E-4 fC. (b)  $V_{GS}/V_{DS}$ -*d* characteristics with  $Q_d$  of 1.0E-4 fC.

#### **Supporting Information Note 1**

Electrostatic discharge (ESD) is a major concern in advanced MOSFET devices. Triboelectric contact electrification is invariably prone to ESD events. Since our tribotronic transistors utilize triboelectric contact electrification and electrostatic induction to produce an electrostatically induced gate-source voltage  $V_{GS}$  acting as the gate voltage, it is definitely important to concern the electrostatic discharge (ESD) problem. In our tribotronic transistors, the major concern relating to ESD is the electrostatically induced voltages ( $V_{GS}$  in TPG NMOS,  $V_{GS}$  and  $V_{DS}$  in TPD NMOS), which are mainly dependent on the triboelectric charge amount Q and the separation distance d.

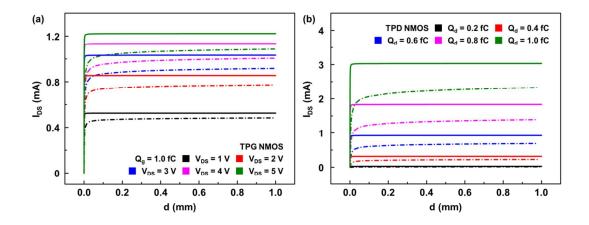

First, it is of great importance to control the electrostatically induced voltages being capable of driving the transistors but not causing ESD. The main concern is the effective control of the triboelectric contact electrification process, which determines the triboelectric charge amount Q. According to the simulated results shown in Figure S8, for both TPG and TPD NMOS operated at "w/o feedback" and "w/ feedback" modes, the I<sub>DS</sub> as well as V<sub>GS</sub> finally saturates to a maximum value (I<sub>DS,max</sub> and V<sub>GS,max</sub>) when separation distance d is as large as 1 mm. The V<sub>GS,max</sub> is independent of the separation distance d and is determined by the triboelectric gate charge Q<sub>g</sub>. Therefore, the minimum triboelectric gate charge Q<sub>g,min</sub> needed to drive the tribotronic transistors is determined by the condition V<sub>GS,max</sub> = V<sub>th</sub>. Here we only discuss the tribotronic transistors operated at "w/o feedback" mode. As illustrated in Figure S9a, the transferred charge Q equals the gate charge Q<sub>g</sub> when the d is infinite, and then the charge distribution model can be simplified to the right part of Figure S9a. Under this condition, the

$V_{GS}$  is the maximum  $V_{GS,max}$  and its relation with the gate charge  $Q_g$  can be easily derived as follow:

$$Q_g = CV_{GS,max}$$

where  $C = \frac{C_{GD}C_{Si}}{C_{GD}+C_{Si}}$  is the capacitance between the two electrodes,  $C_{GD}$  and  $C_{Si}$  are the capacitances of the gate dielectric and the silicon, respectively. Thus, the minimum gate charge  $Q_{g,min}$  is:

$$Q_{g,min} = \frac{C_{GD}C_{Si}}{C_{GD} + C_{Si}}V_{th}$$

where  $V_{th}$  is the threshold voltage of transistors, which is 0.8 V in our simulation model. Then the Q<sub>g,min</sub> and corresponding triboelectric gate surface charge density  $\sigma_{g,min}$  are derived as ~0.12 fC and ~80  $\mu$ C m<sup>-2</sup>.

The triboelectric surface charge density can be tuned/controlled by choosing appropriate mobile polymer materials according to the triboelectric series.<sup>1</sup> Moreover, surface functionalization<sup>2</sup> and modification<sup>3</sup> are two alternatives to control the triboelectric surface charge density. By these methods, we can carefully control the triboelectric gate surface charge density  $\sigma_g$  to produce V<sub>GS</sub> over V<sub>th</sub> for driving tribotronic transistors, but not to produce too large V<sub>GS</sub> resulting in ESD problem.

Second, if the triboelectric gate surface charge density  $\sigma_g$  is too large beyond our expectation in practice and damages the tribotronic transistors, we can also design the tribotronic transistors with stacked gate dielectrics, as shown in Figure S9b. By stacking a thick (from tens of nanometers to even a few microns) high- $\kappa$  dielectric over the conventional gate dielectric, only a small fraction of the total voltage caused by the triboelectric gate charge Q<sub>g</sub> is applied across the conventional gate dielectric, while the rest is applied across the high- $\kappa$  dielectric. In this manner, ESD problems can also be prevented.

**Figure S8.** (a)  $I_{DS}$ -d characteristic of triboelectric-potential gated (TPG) NMOS with  $Q_g = 1.0$  fC and  $V_{DS}$  bias from 1 to 5 V. (b)  $I_{DS}$ -d characteristic of self-powered triboelectric-potential driven (TPD) NMOS with  $Q_d$  from 0.2 to 1.0 fC. Conduction channel length  $L = 1 \mu m$ . Solid lines and dash dot lines correspond to the "with feedback" (w/ feedback) mode and the "without feedback" (w/o feedback) mode, respectively.

Figure S9. (a) Charge distribution in tribotronic transistors operated at "w/ feedback" mode.

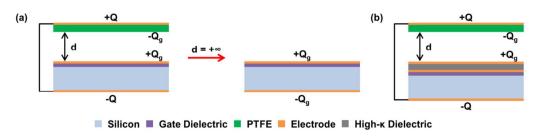

(b) Tribotronic transistors with stacked gate dielectric.

### **Supporting Information Note 2**

We have simulated the triboelectric-potential gated (TPG) NMOS and the self-powered triboelectric-potential driven (TPD) NMOS with carrier mobility degradation by taking the effects of phonons, impurities, surface scattering and high electric field velocity saturation on carrier mobility into consideration.

In practice, the mobility is typically computed using analytic functions with or without a rigorous physical motivation and designed to fit the experimental data to a good degree of accuracy. Often, mobility models are designed to address one particular effect and require other mobility models as a basis. As an example, high electric field effects are often incorporated into a model by defining the high electric field mobility as a function of the mobility due to phonon and impurity scattering. Here, we combine phonon, impurity, surface scattering and high electric field mobility models in the following manner:

$$\mu_{tot} = \mu_E \big( \mu_S(\mu_{PI}) \big) \tag{1}$$

where  $\mu_{tot}$  is the total mobility,  $\mu_E$ , the mobility due to high electric field effects, is a function of  $\mu_S$  (the mobility due to surface scattering), which in turn is a function of  $\mu_{PI}$  (the mobility due to phonon and impurity scattering).

The empirical mobility model derived by N.D. Arora et al.<sup>4</sup> is employed to include both phonon and impurity scattering. The electron  $(\mu_{n,PI})$  and hole  $(\mu_{p,PI})$  mobilities are determined by the equations:

$$\begin{cases} \mu_{n,PI} = \mu_{min,n} + \frac{\mu_{0,n}}{1 + \left(\frac{N}{N_{0,n}}\right)^{\alpha}} \\ \mu_{p,PI} = \mu_{min,p} + \frac{\mu_{0,p}}{1 + \left(\frac{N}{N_{0,p}}\right)^{\alpha}} \end{cases}$$

(2)

$$\begin{cases} \mu_{min,n} = \mu_{min,n}^{ref} \left(\frac{T}{T_{ref}}\right)^{\beta_1} \\ \mu_{min,p} = \mu_{min,p}^{ref} \left(\frac{T}{T_{ref}}\right)^{\beta_1} \end{cases}$$

(3)

$$\begin{cases} \mu_{0,n} = \mu_{0,n}^{ref} \left(\frac{T}{T_{ref}}\right)^{\beta_2} \\ \mu_{0,n} = \mu_{0,n}^{ref} \left(\frac{T}{T_{ref}}\right)^{\beta_2} \end{cases}$$

$$\tag{4}$$

$$\left(N_{0,n} = N_{0,n}^{ref} \left(\frac{T}{T_{ref}}\right)^{\beta_3}$$

$$(5)$$

$$\left(N_{0,p} = N_{0,p}^{ref} \left(\frac{1}{T_{ref}}\right)\right) \\

\alpha = \alpha_0^{ref} \left(\frac{T}{T_{ref}}\right)^{\beta_4}$$

(6)

$$N = N_a^- + N_d^+ \tag{7}$$

where T is the lattice temperature,  $N_a^-$  is the ionized acceptor concentration, and  $N_d^+$  is the ionized donor concentration. All the other parameters are the silicon material properties, which are taken from Ref. 4.

Then, the surface scattering mobility  $(\mu_S)$  resulting from surface acoustic phonons and from surface roughness is combined with the phonon and impurity mobility  $(\mu_{PI})$ . The electron  $(\mu_{n,S})$  and hole  $(\mu_{p,S})$  mobilities are determined by the following equations:<sup>5</sup>

$$\begin{cases} \frac{1}{\mu_{n,S}} = \frac{1}{\mu_{n,PI}} + \frac{1}{\mu_{n,ac}} + \frac{1}{\mu_{n,sr}} \\ \frac{1}{\mu_{p,S}} = \frac{1}{\mu_{p,PI}} + \frac{1}{\mu_{p,ac}} + \frac{1}{\mu_{p,sr}} \end{cases}$$

(8)

$$\begin{cases} \mu_{n,ac} = \frac{\mu_{n,1}}{\left(\frac{E_{\perp,n}}{E_{ref}}\right)} + \frac{\mu_{n,2} \left(\frac{N}{N_{ref}}\right)^{\alpha_{n}}}{\left(\frac{E_{\perp,n}}{E_{ref}}\right)^{1/3} \left(\frac{T}{T_{ref}}\right)} \\ \mu_{p,ac} = \frac{\mu_{p,1}}{\left(\frac{E_{\perp,p}}{E_{ref}}\right)} + \frac{\mu_{p,2} \left(\frac{N}{N_{ref}}\right)^{\alpha_{p}}}{\left(\frac{E_{\perp,p}}{E_{ref}}\right)^{1/3} \left(\frac{T}{T_{ref}}\right)} \\ \end{cases}$$

(9)

$$\begin{cases} \mu_{n,sr} = \frac{\delta_{n}}{E_{\perp,n}^{2}} \\ \mu_{p,sr} = \frac{\delta_{p}}{E_{\perp,p}^{2}} \end{cases}$$

(10)

$$N = N_a^- + N_d^+ \tag{11}$$

where *T* is the lattice temperature,  $N_a^-$  is the ionized acceptor concentration, and  $N_d^+$  is the ionized donor concentration,  $E_{\perp,n}$  is the component of the electric field perpendicular to the electron current, and  $E_{\perp,p}$  is the component of the electric field perpendicular to the hole current. All the other parameters are the silicon material properties, which are taken from Ref.

5.

At last, the high electric field mobility ( $\mu_E$ ) is included by utilizing the surface scattering mobility ( $\mu_S$ ) as the basis. The electron ( $\mu_{n,E}$ ) and hole ( $\mu_{p,E}$ ) mobilities are determined by the following equations:<sup>6</sup>

$$\begin{cases}

\mu_{n,E} = \frac{\mu_{n,S}}{\left(1 + \left(\frac{\mu_{n,S}F_n}{v_{n,sat}}\right)^{\alpha_n}\right)^{1/\alpha_n}} \\

\mu_{p,E} = \frac{\mu_{p,S}}{\left(1 + \left(\frac{\mu_{p,S}F_p}{v_{n,sat}}\right)^{\alpha_p}\right)^{1/\alpha_p}}

\end{cases}$$

(12)

$$\begin{cases} \alpha_n = \alpha_{n,0} \left(\frac{T}{T_{ref}}\right)^{\beta_{n,1}} \\ \alpha_p = \alpha_{p,0} \left(\frac{T}{T_{ref}}\right)^{\beta_{p,1}} \end{cases}$$

(13)

$$\begin{cases} v_{n,sat} = v_{n,0} \left(\frac{T}{T_{ref}}\right)^{\beta_{n,2}} \\ v_{p,sat} = v_{p,0} \left(\frac{T}{T_{ref}}\right)^{\beta_{p,2}} \end{cases}$$

(14)

where *T* is the lattice temperature,  $F_n = E_{\parallel,n}$  and  $F_p = E_{\parallel,p}$  currently are the driving forces for electrons and holes,  $E_{\parallel,n}$  is the component of the electric field parallel to the electron current, and  $E_{\parallel,p}$  is the component of the electric field parallel to the hole current. All the other parameters are the silicon material properties, which are taken from Ref. 6.

By linking different mobility models together as described above, we use the electron  $(\mu_n = \mu_{n,E})$  and hole  $(\mu_p = \mu_{p,E})$  mobilities, which contain all the contributions from the phonon, impurity, surface scattering and high electric field, in the simulation. Mobility models generally model the processes that remove or limit the momentum of carriers;

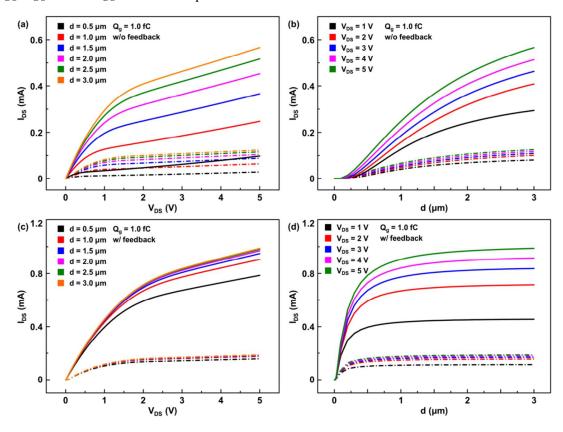

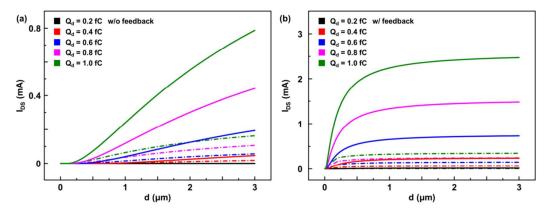

therefore a reduction in the drain-source current  $I_{DS}$  is expected when they are included in the simulation. Figure S10 and S11 show the results with constant mobility (solid lines) and with the added mobility models (dash dot lines) of TPG NMOS (Figure S10) and TPD NMOS (Figure S11), respectively. Obviously, for both TPG NMOS and TPD NMOS operated at "w/o feedback" mode and "w/ feedback" mode, the  $I_{DS}$  is significantly reduced; while the  $I_{DS}$ -V<sub>DS</sub> and the  $I_{DS}$ -d relationships are still the same.

**Figure S10.** Characteristics of triboelectric-potential gated (TPG) NMOS with gate charge  $Q_g = 1.0$  fC.  $I_{DS}$ - $V_{DS}$  characteristics of TPG NMOS with separation distance d from 0.5 to 3.0  $\mu$ m under (a) "w/o feedback" mode and (c) "w/ feedback" mode, respectively.  $I_{DS}$ -d characteristics of TPG NMOS with drain-source voltage  $V_{DS}$  from 1 to 5 V under (b) "w/o feedback" mode and (d) "w/ feedback" mode, respectively. Conduction channel length L = 1  $\mu$ m. Solid lines and dash dot lines correspond to the simulated results without and with

considering the mobility models, respectively.

**Figure S11.** Characteristics of self-powered triboelectric-potential driven (TPD) NMOS with drain charge  $Q_d$  from 0.2 to 1.0 fC. I<sub>DS</sub>-d characteristics of self-powered TPD NMOS under (a) "w/o feedback" mode and (b) "w/ feedback" mode, respectively. Conduction channel length  $L = 1 \mu m$ . Solid lines and dash dot lines correspond to the simulated results without and with considering the mobility models, respectively.

## References

1. Wang, Z. L., Triboelectric Nanogenerators as New Energy Technology for Self-Powered Systems and as Active Mechanical and Chemical Sensors. *ACS Nano* **2013**, *7*, 9533-9557.

Wang, S.; Zi, Y.; Zhou, Y. S.; Li, S.; Fan, F.; Lin, L.; Wang, Z. L., Molecular surface functionalization to enhance the power output of triboelectric nanogenerators. *Journal of Materials Chemistry A* 2016, 4, 3728-3734.

Jeong, C. K.; Baek, K. M.; Niu, S. M.; Nam, T. W.; Hur, Y. H.; Park, D. Y.; Hwang, G. T.; Byun, M.; Wang, Z. L.; Jung, Y. S.; Lee, K. J., Topographically-Designed Triboelectric Nanogenerator *via* Block Copolymer Self-Assembly. *Nano Lett.* 2014, 14, 7031-7038.

4. Arora, N. D.; Hauser, J. R.; Roulston, D. J., Electron and Hole Mobilities in Silicon as a Function of Concentration and Temperature. *IEEE Trans. Electron Devices* **1982**, 29, 292-295.

5. Lombardi, C.; Manzini, S.; Saporito, A.; Vanzi, M., A Physically Based Mobility Model for Numerical-Simulation of Nonplanar Devices. *Ieee T Comput Aid D* **1988**, 7, 1164-1171.

6. Canali, C.; Majni, G.; Minder, R.; Ottaviani, G., Electron and Hole Drift Velocity-Measurements in Silicon and Their Empirical Relation to Electric-Field and Temperature. *IEEE Trans. Electron Devices* **1975**, 22, 1045-1047.